主题中讨论的其他器件: TCA9509

您好!

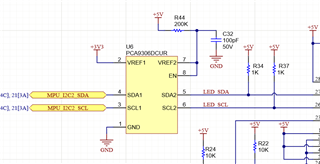

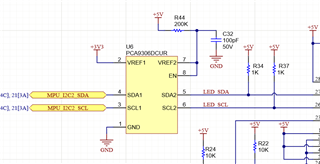

在设计中使用 PCA9306、我想知道通过 SDA/SCL 引脚是否存在反馈电流问题。

在此设计中、+5V 首先上升、几毫秒后+3V3随之上升。 我知道从 VREF2到 VREF1会有一些泄漏、受200K 的限制。 那么、SDA 和 SCL 信号的泄漏会怎样呢? 5V 上拉电阻器上是否存在从 SDA2到 SDA1、或从 SCL2到 SCL2的泄漏电流?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

在设计中使用 PCA9306、我想知道通过 SDA/SCL 引脚是否存在反馈电流问题。

在此设计中、+5V 首先上升、几毫秒后+3V3随之上升。 我知道从 VREF2到 VREF1会有一些泄漏、受200K 的限制。 那么、SDA 和 SCL 信号的泄漏会怎样呢? 5V 上拉电阻器上是否存在从 SDA2到 SDA1、或从 SCL2到 SCL2的泄漏电流?

谢谢!

尊敬的 Oliver:

是的、在正常运行期间会有泄漏电流流流回器件的下侧。 当逻辑低电平通过器件传播时、内部 FET 在本质上充当强电阻器。 该泄漏电流将从5V 电源流过器件、然后流回3.3V 侧。 请注意、当传播逻辑高电平时、内部 FET 将处于开路连接、因此1侧与2侧完全隔离、允许外部上拉电阻上升到其电压。

如果需要更低的功耗、则需要相应地调整外部上拉电阻器的大小、从而能够实现该功能(不过、会对速度进行折衷、因此您的最大可实现数据速率将受到限制)。

以下应用手册 深入介绍了如何计算上拉电阻器的值:

此致、

插孔

嗨、Olivier、

感谢您澄清了您的问题。 您的怀疑是正确的、因为当首先加电5V 电源、然后是3.3V 电源时、2侧到1侧会出现泄漏。 这是由于 EN 引脚短接至 VREF2电源、因此在5V 电源斜升时将启用该器件。 未通电后、1侧的电压实际上将为0V、这进一步导致 FET 在线性区域工作、此时将有电流流过 FET。

如果需要考虑这一点、是否可以使用备选项在外部控制 EN 引脚。 同样重要? (请记住、EN 引脚上的电压必须至少比 VREF1高0.7V)。

此致、

插孔