主题中讨论的其他器件: TCA9517

您好,

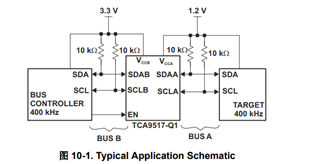

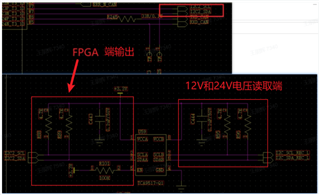

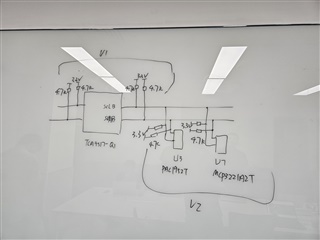

下图显示了 TCA9517-Q1的原理图。 端口 A 和端口 B 使用相同的电源、上拉电阻器为4.7K。 FPGA 驱动 IIC。 端口 A 和端口 B 引脚 SCL 和 SDA 的输出电压均为高电平。 100个电路板中有6个存在此类问题。 请帮您查看原理图并分析原因;

基于上述问题、客户进行了以下测试、请参阅。

1. 更换为新设备,IIC 输入和输出电平正常;

2.使端口 A 和端口 B 的电源(3.3V)独立, IIC 输入和输出电平为正常;

3。端口 B 具有三组上拉电阻器。 删除任意一组或两组, IIC 输入和输出电平均为正常;

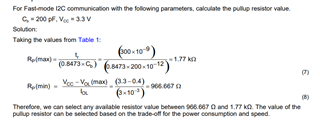

4. 通过改变端口 A 或端口 B 上拉电阻的电阻值,例如将其改为11K,通过改变端口 A 或端口 B 上拉电阻的电阻值,例如将其改为11K, IIC 输入和输出电平是正常的。 对于上拉电阻值?Ω 的选择是否有任何建议或计算公式

谢谢!