大家好!

我想问两个问题。

1) 1)它是否是施密特触发输入、如 SNx4 系列逻辑 IC?

2)什么是 I/O 端口的上升/下降时间? 有限值吗?

为了降低噪音、我将连接输入电容。

我想知道可以增加多少个输入电容器的负载电容。

如果您告诉我参考值、我将不胜感激。

此致、

Ryusuke。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好!

我想问两个问题。

1) 1)它是否是施密特触发输入、如 SNx4 系列逻辑 IC?

2)什么是 I/O 端口的上升/下降时间? 有限值吗?

为了降低噪音、我将连接输入电容。

我想知道可以增加多少个输入电容器的负载电容。

如果您告诉我参考值、我将不胜感激。

此致、

Ryusuke。

您好,Ryusuke,

Unknown 说:1)它是像 SNx4 系列逻辑 IC 这样的施密特触发输入吗?

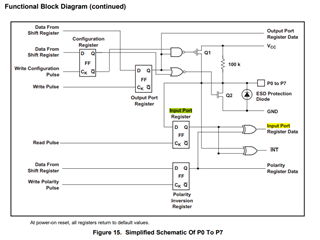

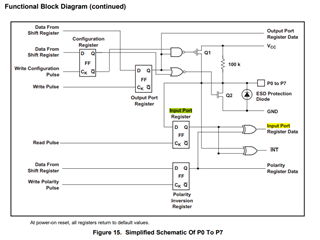

i2c 输入监测输入的电压电平。 输入高逻辑被视为 VCC 的70%。 输入低电平逻辑被视为 VCC 的30%。 根据 I2C 标准、中30%至70%之间的精度尚不确定。 这两个值相距足够远、可以充当较大的迟滞、因此噪声不会意外切换边沿情况的输入。

2)什么是 I/O 端口的上升/下降时间? 有限值吗?

为了降低噪音、我将连接输入电容。

我想知道可以增加多少个输入电容器的负载电容。

如果您告诉我参考值、我将不胜感激。

[/报价]I/O 端口上的上升/下降时间没有限制、电压取决于触发器记录的逻辑值是高还是低。

用于降低噪声的输入电容器连接没有问题、只需确保其符合 I2C 标准即可。 I2C 的最大总线电容限值为400pF (SCL 为400pF、SDA 为400pF)。 添加高于400pF 的滤波电容器在技术上会将 I2C 总线超出规格、并可能导致上升时间问题、以及信号在采样前无法上升至 VIH、从而可能导致数据损坏。

我已经随附了一个应用手册、其中介绍了如何根据总线电容、VOL、IOL、数据速率等参数选择上拉电阻器。 调整 I2C 上的电阻和电容大小会直接影响 I2C 总线上的 VOL 和上升时间。

此致、

泰勒

您好,Ryusuke,

这句话是什么意思?

我想知道参考它。

您在谈论数据表的更改吗?

此致、

泰勒

您好,Ryusuke,

无论迟滞如何、输入电压都符合 I2C 标准 VCC 的30%或 VIH=70%或 VCC 的80%。 VIL 和 VIH 之间存在很大的裕度、因此我不希望增加的噪声会在高逻辑和低逻辑之间切换输入、从而损坏数据。

例如...

一旦注册了低逻辑输入、它就不会变成高逻辑输入、直到内部输入端口寄存器中 VCC 的70%。 数据表可向您保证、一旦输入达到 VCC 的70%、就会在输入端口寄存器中读取到逻辑高电平(1)。 相反、当输入端的逻辑高电平信号开始下降时、只有当输入降至30% VCC 以下时、输入端口寄存器中的数据才会发生变化。

这基本上在某种意义上类似于迟滞。

此致、

泰勒