Other Parts Discussed in Thread: TCA9535

您好。专家

该工程计划使用 TCA9535进行设计、预计将使用8个 TCA9535。我阅读了技术手册(SLVA689)。文档中有一些问题、请予以帮助。

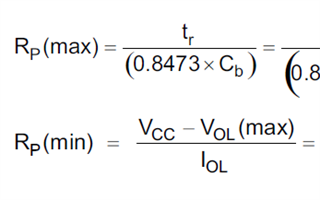

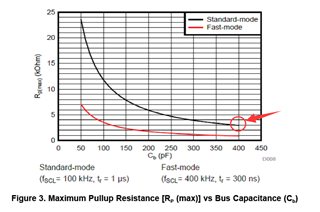

1 μ F 如何在、中确定总线电容 Cb 的值?

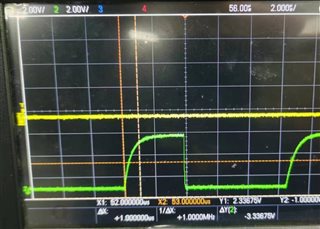

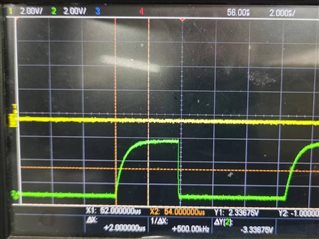

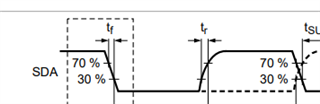

2、μ s 在 SLVA689中、fSCL=100kHz、TR=1us、fSCL=400kHz、TR=300ns、如果 fSCL 是其他频率、如何确定 TR 的值? 例如、fSCL=10kHz、TR 等于?

、我使用8个 TCA9535、是否可以为 SDA 和 SCL 分别使用1个上拉电阻器? 或者我需要使用多个上拉电阻器吗? 在执行 PCBLAOUT 时、上拉电阻器的正确放置是什么?

谢谢你。