Other Parts Discussed in Thread: SN65LVDS105, SN65LVDS116

主题中讨论的其他器件:SN65LVDS105、

我有一个设计、我计划使用64MHz CMOS 振荡器生成参考时钟、然后将其引入 SN65LVDS105 (CMOS 到4x LVDS)。 然后、SN65LVDS105的三个输出进入三个 SN65LVDS116、总共可创建48个 LVDS 时钟。 这48个 LVDS 时钟连接到48个 PCIe 类型的连接器(板对板、无布线)、可以插入也可以不插入。

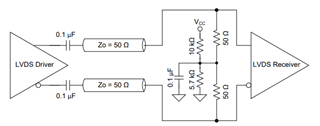

我希望确保正确端接接收器、但数据表中不清楚 建议使用哪些外部元件。 我甚至不知道 SN65LVDS116 接收器是否具有内部端接(图12似乎表明它是内部的、但"等效 输入和输出 原理图"似乎表明它没有内部端接)。

您能否就 SN65LVDS105 和我的 SN65LVDS116之间的 LVDS 线路上 以及 SN65LVDS116 和子板上的接收器之间的内容提供一些指导?

- 交流耦合电容器? 如果是、这些驱动器的最佳位置是什么(靠近驱动器、靠近接收器、靠近主板上的连接器、靠近子板上的连接器)?

- 直流偏置电阻器?

- 共模扼流圈(例如 DLW21SZ900HQ2L 或类似产品)? 放置它的最佳位置在哪里?

- 串联电阻器?

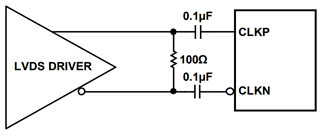

- 终止方案? 例如、电阻仅为100欧姆、或者50至50并使用电容器接地?

我见过几个显示不同方案(例如 SLAA840)用法的应用手册、但我想知道建议针对此应用采用哪种设置。

请注意、子板的接收器需要外部端接电阻器和100nF 电容器: