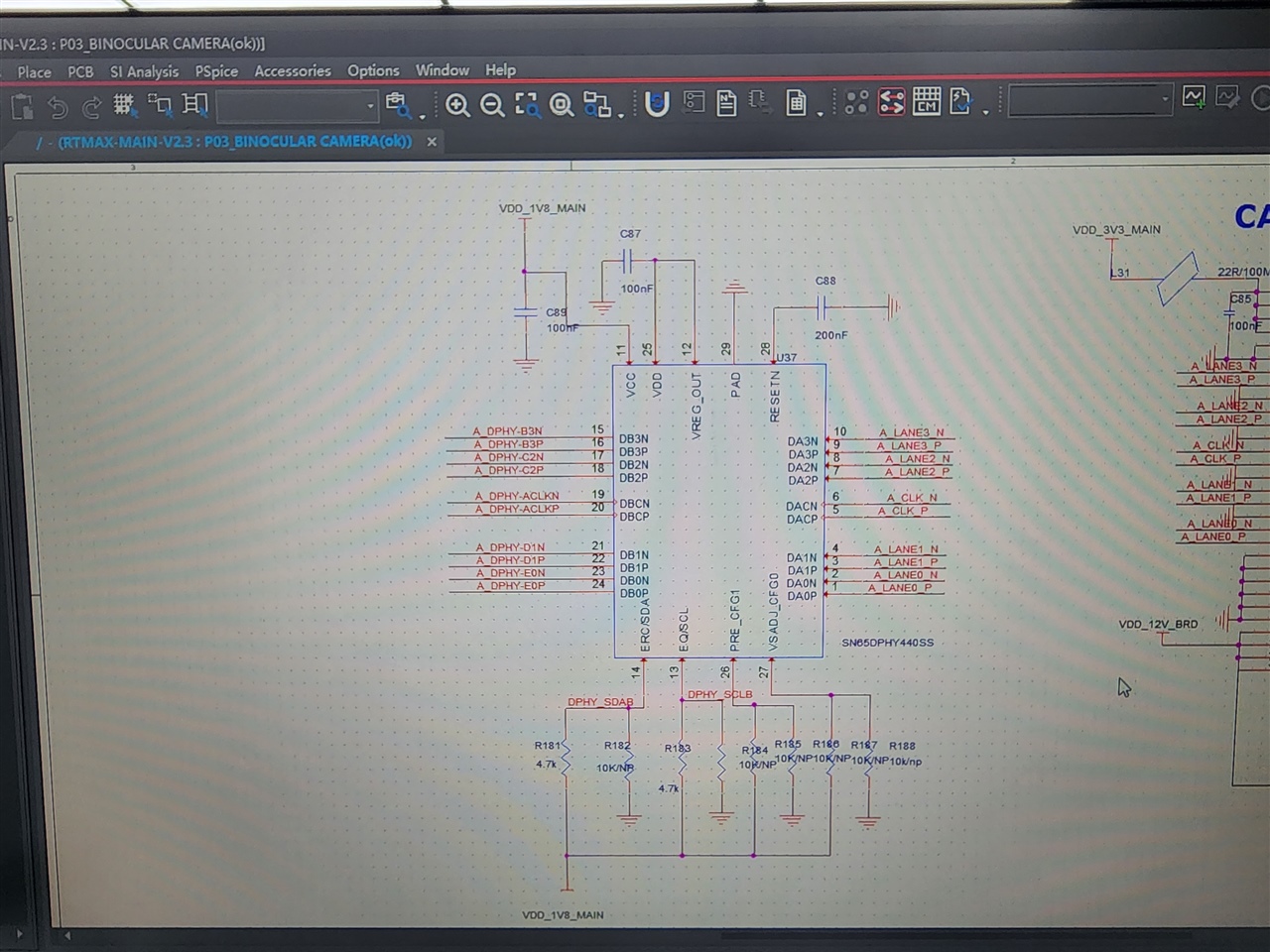

我们目前正在努力将 SN65DPHY440 MIPI 中继器 IC 集成到我们的设计中、并遇到了之前提到的 lane 0的问题。

1.我们尝试按照以下建议对寄存器进行设置:

为 HS TX 路径写入寄存器0x50并启用8'h01 //覆盖

在启用8'h01 //HS TX 路径的情况下写入寄存器0x51。

使用8'h1E 写入寄存器0x61 //禁用通道0的 LP 路径

为 HS RX 路径写入寄存器0x70并启用8'h01 //覆盖

在 启用8'h01 // HS RX 路径的情况下写入寄存器0x71。

我们仍然会看到从通道0读取的错误数据、我们认为这是由于其他通道正确地从 LP 模式转换到 HS、而通道0保持为 HS 模式所致。

然后我们尝试了:

为 HS TX 路径写入寄存器0x50并启用8'h1f //覆盖

在 启用8'h1f //HS TX 路径的情况下写入寄存器0x51。

为寄存器0x61写入8'h00 //为所有通道禁用 LP 路径

为 HS RX 路径写入寄存器0x70并启用8'h1f //覆盖

在8'h1f // HS RX 路径启用时写入寄存器0x71。

并且我们会在所有通道上获得错误的数据读取。

有任何解决此问题的建议吗?

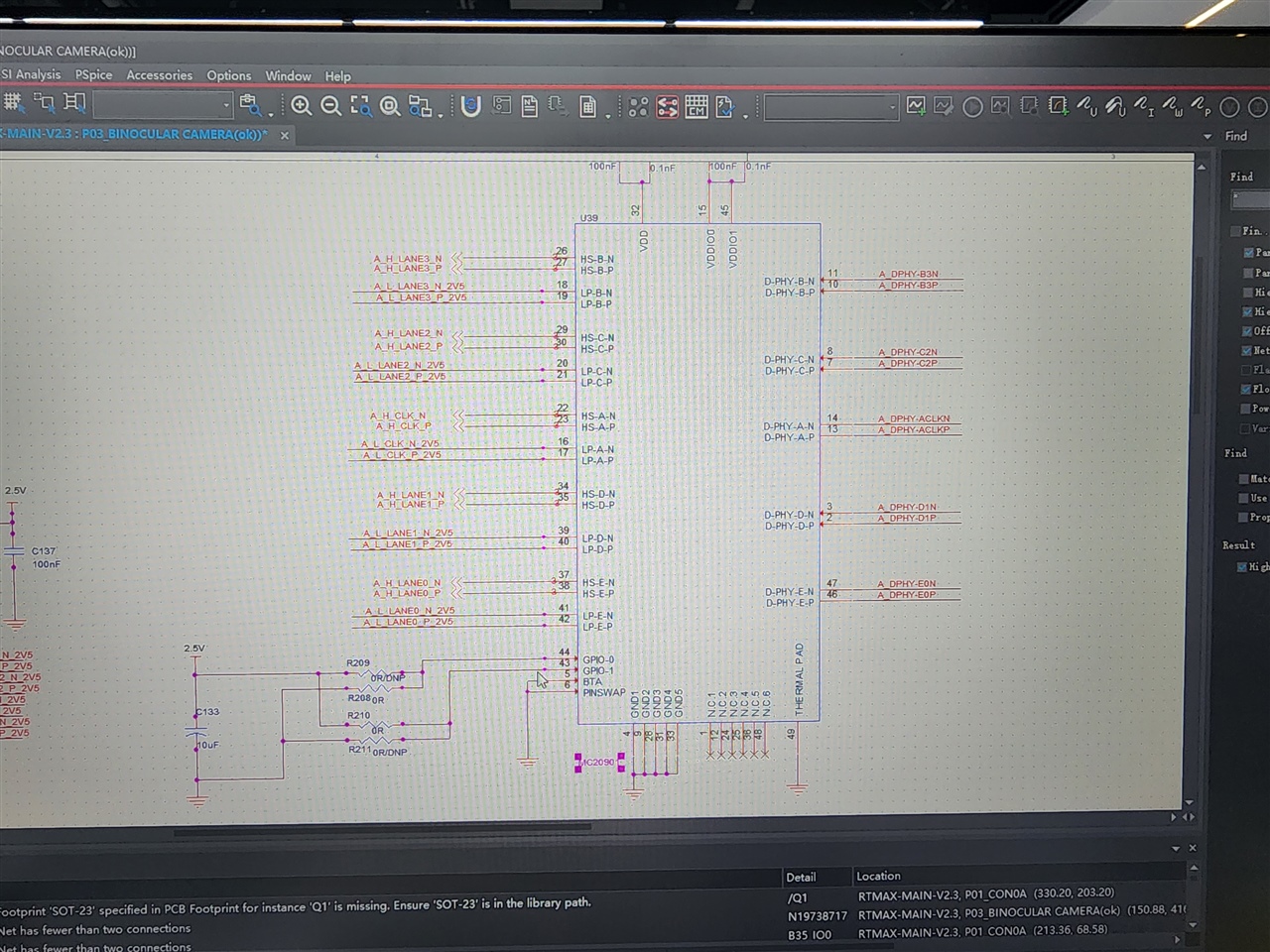

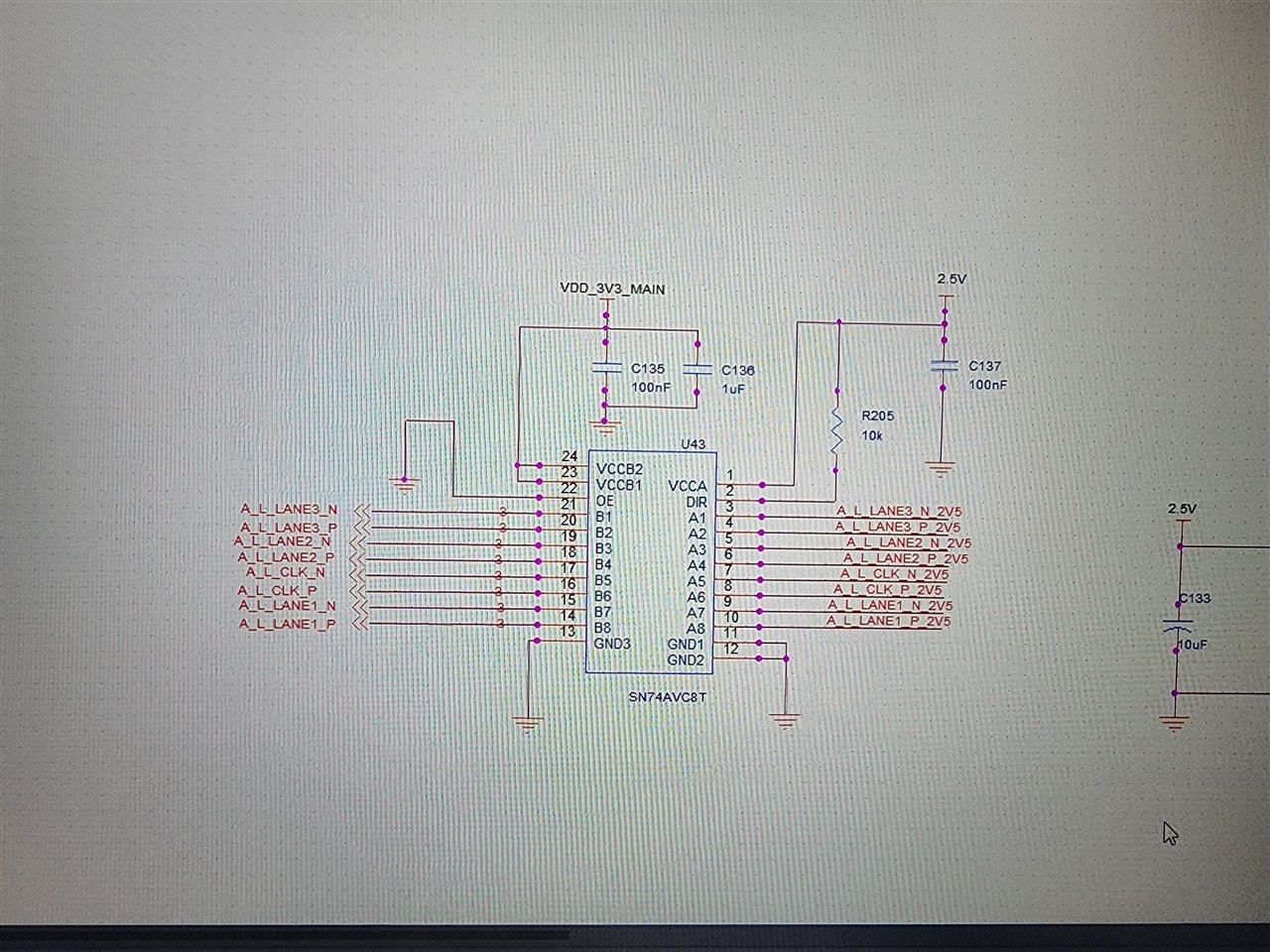

2.此外,我们目前正在计划添加一个来自 Meticom 的 MIPI DPHY MC20901 IC ,它将连接到 SN65DPHY440的 TX 端,我想询问这是否会通过提供与通道0 TX 的未端接连接来解决通道0的问题。

3.是否有可能让两个 SN65DPHY440并行连接、具有相同的时钟源、但在未使用通道0的情况下?