Other Parts Discussed in Thread: DS90CF384A, DS90C383, DS90CF384

主题中讨论的其他器件: DS90C383、

您好!

我是 Tanveer Ahmed、来自印度班加罗尔 TATA Advanced Systems。

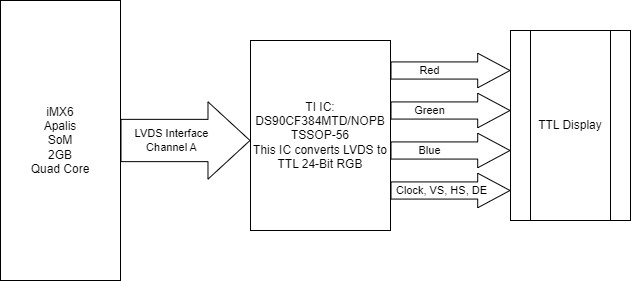

我在设计中使用 DS90CF384MTD/NOPB (TSSOP-56)、以便将 LVDS 转换为24位 TTL 逻辑。

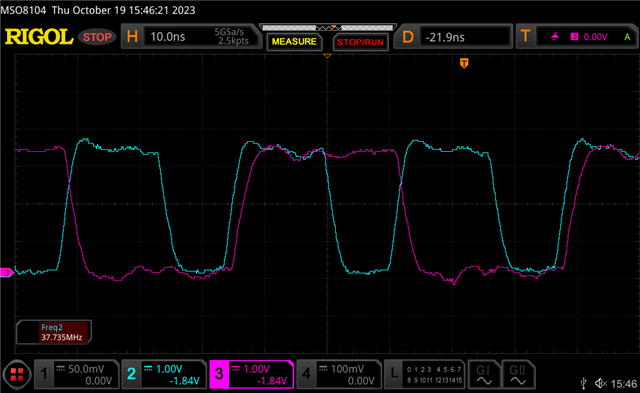

我希望数据应在上升沿进行采样、或者将其更改为下降沿。

如何将该数据样本从时钟的下降沿更改为时钟的上升沿、或反之?

在数据表第11页中、我可以看到在时钟的正边沿或负边沿对数据进行采样。

请尽早提出建议。

谢谢!