主题中讨论的其他器件:AM2432

大家好、

这是 AM2432+DP83826中的客户第一个设计。

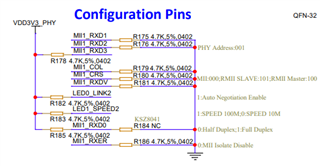

请帮助审查设计。 重点对接口/config/时钟进行检查。 有2个 MII 网络端口和2个 RMII 从网络端口。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Minghao:

您能要求客户填写我们的原理图检查清单吗? 填写完毕后、请返回给我、我可以对其进行审核(最多需要1个工作周)。

e2e.ti.com/.../8484.DP83826_5F00_Schematic_5F00_Design_5F00_Review_5F00_Checklist.xlsx

此致、

阿尔瓦罗

尊敬的 Reyes:

这是我的客户反馈。

请帮助您进行本次原理图审阅。

e2e.ti.com/.../7002.DP83826_5F00_Schematic_5F00_Design_5F00_Review_5F00_Checklist.xlsx

尊敬的 Minghao:

我看到这里有4个 PHY 需要审查、我没有进行完整的原理图审查、我只看了束带和时钟。 我将根据原理图中的标签、在下面提供意见。 附件是 带备注的原理图检查清单、我仅检查了 D11。 如果您有任何其他需要我查看的内容、请告诉我。

e2e.ti.com/.../DP83826_5F00_Schematic_5F00_Checklist_5F00_D11.xlsx

所有4个 PHY 都配置为基本模式

所有搭接

________________________________________________________________

D11:

PHY ID 001、 正确搭接

COL & RX_DV 被拉至高电平、RMII_SLAVE 被启用。

XI 正在 接收 50 MHz CLK、 这 对于 RMII_SLAVE 是正确的

________________________________________________________________

D13:

PHY ID 010、捆绑 正确

COL & RX_DV 被拉至高电平、RMII_SLAVE 被启用。

XI 正在 接收50 MHz CLK、 这 对于 RMII_SLAVE 是正确的

________________________________________________________________

D15:

PHY ID 001、捆绑正确、但这与 D11是同一个 PHY_ID、如果它们都连接到同一个 SoC、这可能会在您的系统中引起问题。

COL 和 RX_DV 被拉至低电平、MII 使能。

XI 正在接收25 MHz CLK、这对于 MII 是正确的

________________________________________________________________

D17:

PHY ID 010、捆绑正确、但这与 D13是同一个 PHY_ID、如果它们都连接到同一个 SoC、这可能会在您的系统中引发问题

COL & RX_DV 被拉至高电平、RMII 从模式

XI 正在接收50 MHz CLK、这对于 RMII 从模式是正确的

此致、

阿尔瓦罗