您好!

我们在 电路板中使用部件 DP83867IRRGZ。

我们发现与 PHY 相连的晶体(ABM8G-25.000MHZ)不提供时钟输入。

我们尝试对 MDIO 进行编程、观察到 PHY 也没有响应。 已检查 PHY 复位输入、PHY 未复位。

您可以帮助说明问题的可能原因吗?

谢谢。此致、

南俊达 M.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们在 电路板中使用部件 DP83867IRRGZ。

我们发现与 PHY 相连的晶体(ABM8G-25.000MHZ)不提供时钟输入。

我们尝试对 MDIO 进行编程、观察到 PHY 也没有响应。 已检查 PHY 复位输入、PHY 未复位。

您可以帮助说明问题的可能原因吗?

谢谢。此致、

南俊达 M.

你好,南俊达,

如果 PHY 未接收到输入时钟、则它将不工作。 时钟本质上是检测信号、因此在尝试其他任何操作之前必须先解决时钟问题。

请参考以下文档、希望这能在将来对您有所帮助。

此致、

阿尔瓦罗

你好,南俊达,

感谢您耐心等待我的回答。

我想总结一下到目前为止的问题、看看我们是否可以重新检查几个方面。

此致、

阿尔瓦罗

你好,南俊达,

我查看了原理图、但没有看到任何问题。 我将再次向您介绍故障排除指南、特别是第3.4节。

您可以在启动期间探测电源、复位、CLKOUT、MDC 和 MDIO 并再次探测稳态吗?

此致、

阿尔瓦罗

你好,南俊达,

以确认我的理解

这是完全没问题的、您现在是否能够读取和写入寄存器?

此致、

阿尔瓦罗

尊敬的 Alvaro:

发现 PHY 有问题。

每当 PHY 获得时钟输入时、它似乎在灌入 MDIO 引脚、并且当 MAC 与 PHY 通信时、MDIO 引脚电压会降至1.1V。 然而、当 PHY 未激活时、即、当时钟输入不存在且 MDIO 被驱动时、MDIO 的电压为1.8V。

有什么可能导致以太网 PHY 出现此类行为的想法吗?

期待很快收到您的回复。

谢谢。此致、

南俊达 M.

尊敬的 Alvaro:

是的、在同一电路板上更换了 PHY。

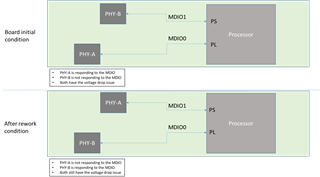

我们有 2个 PHY 连接到 Zynq FPGA。 1 每个连接至 PL 部分(FPGA)、而另一个连接至 PS 部分(处理器)。

我们可以看到两种 PHY 上的常见问题是、一旦为以太网 PHY 提供时钟输入、MDIO 引脚的电压就会从1.8V 下降到1.1V。

我希望您可以从上图中理解、我们将电路板上的 PHY-A 和 PHY-B 位置互换了。

我们可以回答吗、为什么 PHY 上的电压降低了? 当 PHY 未激活(未提供时钟输入)时、MDIO 电压不会降低。

谢谢。此致、

南俊达 M.

你好,南俊达,

此处缺失内容。 处理器的 IO 电压是多少? 您是否曾尝试使用 DP83867EVM 和MSP430 Launchpad 来了解如何读取/写入寄存器? LaunchPad 连接到 EVM 后、 可以使用 USB-2-MDIO 从 PC 读取寄存器。

请提供以下示波器截图

镜头1:

镜头2:

此致、

阿尔瓦罗