Other Parts Discussed in Thread: DS80PCI402

你(们)好

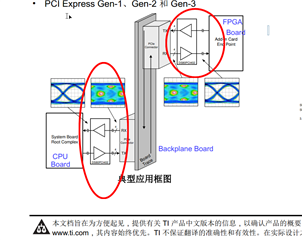

我们正在 三个 PCB 板上设计长 PCIe3.0 x4走线作为背板架构,如下所示(数据表中的快照)。 每 块电路板上的线迹长度约为10cm、因此总共为30cm。

不建议启用两个中继器。 这与上图相冲突。

那么、一个 DS80PCI402是否 足够呢? 它应该 被放置在 CPU 板、背板、还是 FPGA 板上? 如果放置在背板上、则应将其放置在何处?

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: DS80PCI402

你(们)好

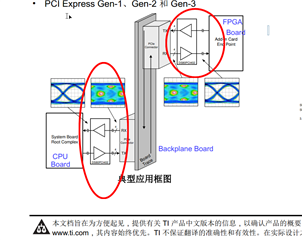

我们正在 三个 PCB 板上设计长 PCIe3.0 x4走线作为背板架构,如下所示(数据表中的快照)。 每 块电路板上的线迹长度约为10cm、因此总共为30cm。

不建议启用两个中继器。 这与上图相冲突。

那么、一个 DS80PCI402是否 足够呢? 它应该 被放置在 CPU 板、背板、还是 FPGA 板上? 如果放置在背板上、则应将其放置在何处?

谢谢。

嗨、BX27:

我建议使用 IBIS AMI 模型来模拟布线上不同位置的一个转接驱动器的场景。 一些答案取决于您的每厘米损耗。您可以使用此链接请求 IBIS AMI https://www.ti.com/product/DS80PCI402#design-development

此致、

尼克

嗨、BX27:

没问题。 我希望你们做得好。 您提到的应用只需要一个转接驱动器、因为您所述的布线长度导致的损耗量低于一个 DS80PCI402的损耗预算。

在何处放置单个转接驱动器的问题。 建议将 转接驱动器放置在损耗最高的一侧、即 CPU 或 FPGA。 此外、我建议使用 IBIS AMI 模型进行仿真仍然适用。

不建议使用两个转接驱动器、因为调优会更加困难。 这两种转接驱动器的情况取决于应用。

此致、

尼克