Other Parts Discussed in Thread: DP83848K, AM4377

主题中讨论的其他器件: AM4377

您好!

我在电路板上使用 DP83848K 和 AM4377、但在某些电路板上会出现一些奇怪的行为。

我曾在处理器论坛上发布过、但并未真正找到解决方案: e2e.ti.com/.../am4377-qspi-flash-for-am4377-uniflash-cli

我的主要问题是、上电时 TX_EN 和 TXD_1到 TXD_3信号会发生什么情况?

根据数据表、这些引脚应仅为输入引脚、但在我的硬件上、这些引脚驱动3.3V。

这些信号也用于 AM4377的自举配置、因此在处理器启动时会使用收发器对其进行驱动。

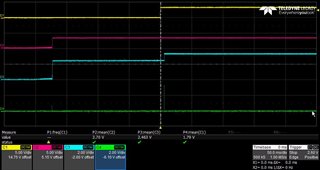

以下是上电时的测量值:

C1:PORz

C2:3V3

C3:ECAT0_TXD0

C4:PHY_RESETn

ECAT0_TXD0信号应该为自举配置的0V、但一旦 PHY 通电、它就会变为大约2.5V、并且当收发器输出(试图将其拉低)被禁用时、它会变为3.3V。

当我完全不为 DP83848K 供电时(引脚1、18、26无电压)、它会按预期工作、TXD0不会被上拉至3.3V。

你有什么建议问题是什么或为什么它的行为是这样的?

非常感谢、此致、

铁莫