主题中讨论的其他器件:SN65DP159、

您好、TI 团队:

我叫 Wesley!

请帮我确认 TMDS181和 SN65DP159原理图?

如有任何疑问 、请告知我。

非常感谢^^

e2e.ti.com/.../VEGA_2D00_3006_5F00_240220_5F00_HDMI_5F00_E2E_5F00_1.pdf

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 团队:

我叫 Wesley!

请帮我确认 TMDS181和 SN65DP159原理图?

如有任何疑问 、请告知我。

非常感谢^^

e2e.ti.com/.../VEGA_2D00_3006_5F00_240220_5F00_HDMI_5F00_E2E_5F00_1.pdf

嘿、Wesley、

很遗憾、我只能进行 U3的原理图审阅。 这是在假设这用于接收端应用的情况下完成的。

我还有几点要说的:

谁是此项目的 OEM/ODM、项目名称是什么?

当前设置处于引脚搭接模式、但无 DDC 侦听功能、可能会出现问题。

确保 CMC 处于所用 HDMI 信号的带宽范围内

确保 ESD 的钳位电压为~5V

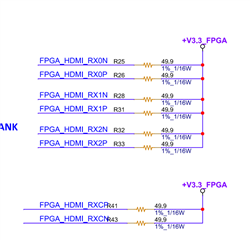

差分信号为什么上拉至3.3V?

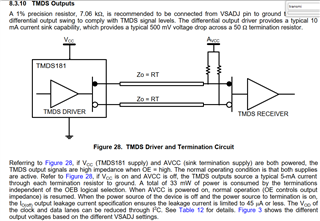

另外、如需接收端应用的参考原理图、请查看 TMDS181数据表第43页: https://www.ti.com/lit/ds/symlink/tmds181.pdf?ts = 1708620111469&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FTMDS181

我将在明天结束 U9和 U6电路的评估并把这些内容提供给您。

谁是该项目的 OEM/ODM,项目名称是什么?--> ODM --> VEGA-3006

当前设置处于引脚搭接模式、但无 DDC 侦听功能、可能会出现问题。

确保 CMC 处于所用 HDMI 信号的带宽范围内-->

"我不知道你在说什么。"

我们目前还有其他项目用于设置 PIN Strap 配置。 反馈的区别在于具有 DDC 侦听功能。

同时在4K 源,它被验证通过!

确保 ESD 的钳位电压为~5V-->

请说明部件号?

差分信号为什么上拉至3.3V?

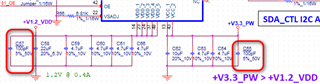

-->由于 TMDS181输出连接到 FPGA,FPGA 没有内部拉高3.3V 引脚类型。 需要外部上拉高电平

请参阅 TMDS181 DS page15

PS:Sch NL/未安装。

谢谢^^

我们目前有其他项目可设置 PIN Strap 配置。 反馈的区别在于具有 DDC 侦听功能。

同时在4K 源,它被验证通过![/报价]我只是想确保具有侦听功能、因为我看不到 DDC 与 FPGA 的连接。

确保 CMC 处于所用 HDMI 信号的带宽内-->看不到您正在使用的共模扼流圈(CMC)的部件号、所以想确保 CMC 对于 HDMI 2.0带宽足够好。 下面是一张图表、其中包含许多 CMC、这些 CMC 将适用于您的应用:

确保 ESD 的钳位电压为~5V->我看了看部分,它应该是好的。

-->由于 TMDS181输出连接到 FPGA,FPGA 没有内部拉高3.3V 引脚类型。 需要外部上拉高电平

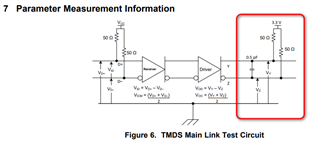

请参阅 TMDS181 DS page15此电路用于参数测量、而非应用用途。 这是交流耦合应用的原理图。 在实践中、它们应该是相同的、但仅供将来参考。

交流耦合实现:

已在原理图底部未看到交流耦合电路、道歉。 然而、HDMI TX1时钟的命名似乎不匹配。

U6的电路与 U3类似、因此上述所有内容也应适用于 U6。 U9原理图审阅。

[/quote]

嘿、Wesley、

下面是 SN65DP159原理图审阅:

以下是我在第一次运行时在原理图审阅时遗漏的一些其他要点。

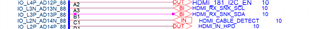

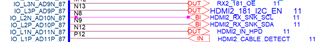

我只是想确保具有侦听功能、因为我看不到 DDC 与 FPGA 的连接。

-->请查看 RX1 U4 & RX2 U7 & TX U10是从 DDC 连接到 FPGA。 我已从 FPGA 确认。

2.看不到您使用的共模扼流圈(CMC)的部件号、所以想要确保 CMC 对于 HDMI 2.0带宽足够好。 下面是一张图表、其中包含许多 CMC、这些 CMC 将适用于您的应用:

我们的 Si 仿真团队建议 HDMI 2.0 RX 端不要使用 CMC,所以我们只能在 HDMI 2.0 TX 端使用 CMC。

此电路用于参数测量、而非应用用途。 这是交流耦合应用的原理图。 在实践中、它们应该是相同的、但仅供将来参考。

-->因为 TMDS 181传输端 DC 终端

,必须处于端子上拉至高49.9欧姆至3.3V。 我们用于尝试将端子拉至高电平49.9欧姆至3.3V。 FPGA 将无法接收

信息。

无论如何、DP159在 TX 端传输交流信号、因此在端子上无需像 TMDS181一样将49.9 Ω 阻抗拉至3.3V。

4.我在原理图底部没有看到交流耦合电路、道歉。 然而、HDMI TX1时钟的命名似乎不匹配。

--> HDMI TX 端必须具有回扫功能,所以 TX FPGA 端参考 CLK 将来自 CLK_GEN

U6电路与 U3类似、因此上述所有内容也应适用于 U6。 U9原理图审阅。

-->Yes!

我修改 RX1、RX2和 TX1电源高频波形电容

RX1、RX2和 TX1新增100pF 电容

感谢您的快速回复^^

我与 FPGA 团队进行的沟通如下:

嘿、Wesley、

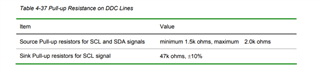

在 TMDS181上,DDC_SDA/SCL 上的40.2k 上拉超出 HDMI 规范,需要使用47k +/-10%-->我们参考 Xilinx EVB 设置为40.2K 欧姆

根据 HDMI 规范、您需要在 DDC 线路上连接一个47k 欧姆的电阻器:

我们无法看到 Xilinx 在内部这些引脚上的作用、因此请咨询它们、确认它们的参考设计符合规格。

FPGA 输入需要交流耦合、但 TMDS181输出需要3.3V 共模电压、因此使用外部50 Ω 端接来设置 CM。但50 Ω 端接和 FGPA 输入端接产生双端接、从而切断输出信号振幅。 可能需要调整 TMDS181输出摆幅以补偿-->我们电路 TMDS181 TMDS 49.9OHM 上拉3.3V-->交流电容-->输入 FPGA MGT 组。

本文指的是上面的图1: