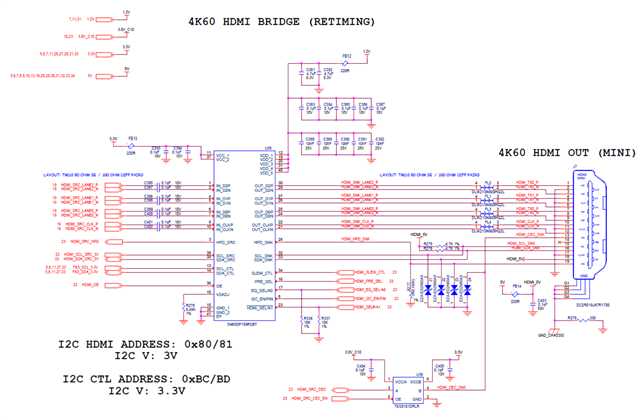

我们正在构建一个视频设备、其中输出信号的源是 Altera FPGA。

问题出在4 N 个通道上是平坦的-这意味着它不是相应 P 的倒数。

引脚为

21 输出_CLKN

22 输出_CLKP

24 输出_D0N

25 输出_D0P

26 输出 D1N

27输出_D1P

28输出_ D2N

29输出_ D2P

所有4个 P 通道都将产生看似正确的信令。 所有4 N 个通道都不产生信号。 当极性翻转时、情况保持不变。 这意味着 P 通道正确、N 通道错误。

这会让我相信与原理图错误相比、存在配置问题。

非常感谢任何帮助或建议。