Other Parts Discussed in Thread: DS125DF111, DS125DF1610, DS100MB203, DS250DF230, USB2ANY, DS125DF111EVM, DS125MB203

主题中讨论的其他器件: DS125DF1610、 DS100MB203、 DS250DF230、 USB2ANY、、 DS125MB203

团队、您好!

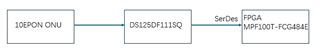

目前、光学模块 ONU 直接连接到 FPGA 的 SerDes 接口、

但光学敏感度只能测量到-31.5dBm (不合格)、需要达到-33dBm。

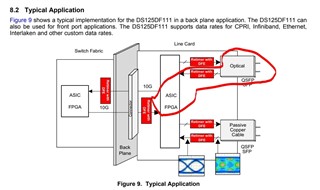

我想使用 DS125DF111SQ、但我不知道我是否可以使用它、我应该注意什么?

FPGA 型号: MPF100T-FCG484E,实际上 FPGA 无法捕捉到10E-3的误差,系统需要被重定时器芯片整形。

谢谢!