请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83848I 您好、专家!

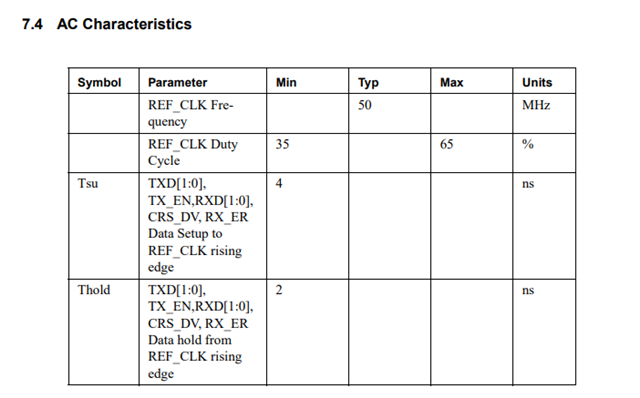

工程师告诉我、他们的 RMII 接口时序不能满足 DP83848的时序规格。 数据表规格要求 TXD 数据设置时间至少为4ns (TXD 至 X1上升)。 它们使用 RMII 将 SOC 连接到 DP83848。 SoC 和 DP83848 x1输入中的 MAC 都由同一个50MHz 源计时。 问题在于他们发现 TXD 数据建立时间(T2.26.2)仅约2ns、无法满足规格(最小4ns)。 他们应该怎么做才能解决此问题? (他们检查了 SOC、似乎无法调整 SOC 中的此时序。)

谢谢!

约翰