主题中讨论的其他器件:ALP、

问题现象:

当 SOC (927 LVDS 输入)设置为54MHz 时、CLK 振幅大约为48mV、但928 LVDS 输出的 CLK 振幅衰减了大约24mV。 与927输入信号不一致的差分频率、当我们将 CLK 频率降低到20MHz 时、927输入和928输出不会衰减。

需要:

LVDS CLK 传输稳定的信号、没有衰减!

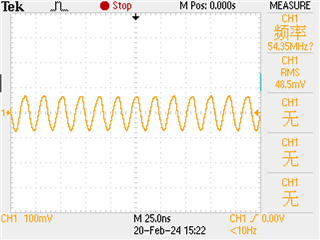

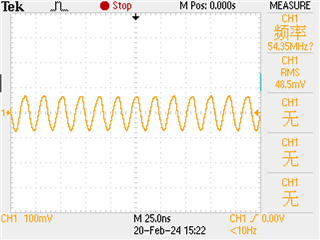

927 LVDS 输入:

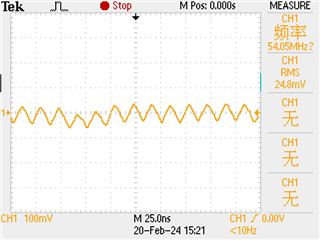

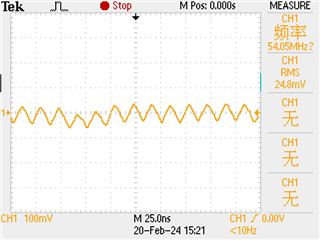

928 LVDS 输出图:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

问题现象:

当 SOC (927 LVDS 输入)设置为54MHz 时、CLK 振幅大约为48mV、但928 LVDS 输出的 CLK 振幅衰减了大约24mV。 与927输入信号不一致的差分频率、当我们将 CLK 频率降低到20MHz 时、927输入和928输出不会衰减。

需要:

LVDS CLK 传输稳定的信号、没有衰减!

927 LVDS 输入:

928 LVDS 输出图:

尊敬的 Shuming:

测量数字信号的经验法则是示波器的带宽应至少为信号频率的5倍。 尽管927和928的测量值在相似的频率下确实具有不同的振幅、但我建议使用更高带宽的示波器进行重新测量(最好是>1GHz 的 BW)。

此应用手册可帮助您查阅有关数字信号测量的经验法则和理论: 链接

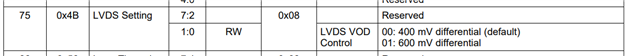

与此同时、增加928输出的 VOD 的一个快速方法就是改变 LVDS 设置(0x4B)寄存器。 在 ALP 或通过 I2C 的情况下为:

board.WriteI2C(928_address,0x4B,0x01)

此致!

插孔

尊敬的 Shuming:

假设这些测量不是在高带宽范围下进行的、并且系统没有潜在问题。 我无法得出结论、928 OLDI 输出存在问题。 如果 LVDS/OLDI 显示器无法正确解读来自928的数据、那么我们可以返回到这个主题。

LVDS 的 TIA/EIA-644-A 标准建议使用5GHz 示波器和至少为100kΩ 差分电阻、差分电容不超过1pF 的示波器探头。

此致!

插孔

尊敬的 Shuming/Dannis:

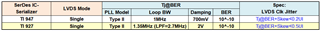

我需要确认要在 DPOJET 中设置的 TI 947参数(不是 TI 927)以进行测量。

对927或947的请求是什么? 这2个器件不使用相同的 PLL 参数。 此 e2e 的标题为" DS90UB928Q-Q1/927 LVDS LK 信号衰减问题"

要获得这些设置、我需要与设计团队同步、以了解如何配置示波器设置来模仿器件 PLL。 因此、请指定此处使用的串行器/解串器。

例如,Loop BW,f/40?Hz 或 KHz?请标出它,谢谢

f 是以 MHz 为单位的 PCLK 频率。

此致、

Fadi A.

尊敬的 Fadi:

如果我们使用 f=loop BW = 1.35MHz、54MHz 2.7MHz)、表中的参数是否正确?

[注释]

TJ@BER 参数设置:目标 BER = 10^-10、PLL 模型=类型 II、环路 BW = 1.35MHz、Damping = 2V、LPF = 2.7MHz、HPF=无

示波器:MSO64B (4GHz、50GS/s)、差动探头:TAP4000 (4GHz)

此致,

舒明