TI 您好:

SOC 端设置的时序如下(1个时钟通道+ 4个数据通道):

H_ACTIVE=1920、HBP = 32、HFP = 48、HSW = 48、v_hACTIVE=720、 Vbp=4、Vfp=4、vsw=8

像素 clk=91Mhz、DSI 速率=600Mbps/通道

设计为948、 我们曾尝试测量948输出的时序、但 该值与我们在 soc 中设置的值不匹配。

请参阅<941 rugup guide.pdf >、其中根据以下公式给出了 DSI 时钟频率和视频 PCLK 之间的转换:F_PCLK =(f_DSI*N_LANES)/12、 f_PCLK =(300*4)/12=100Mhz (计算得出) 概率密度与在 SOC 上设置的91M 不一致。

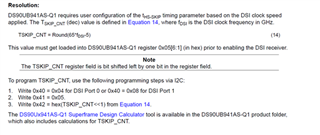

941如何解析 SOC 发送的 DSI 数据? 如何重建时钟、VFP、VBP、HFP、HBP 时间序列?