我们使用 sn65dsi83芯片从双通道 MIPI 转换为 LVDS。

显示面板需要66至70 MHz 范围内的像素时钟。

DSI 只能以83.33 (=500/6)或62.5 (=500/8) MHz 像素时钟输出、这两种时钟都超出规格。

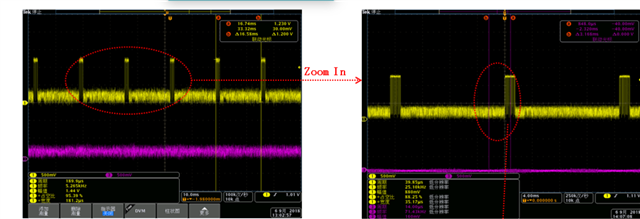

当我们使用 DSI 时钟作为时钟输入时、显示屏工作、图片正常。 尽管像素时钟超出了规格。

REFCLK 输入上有一个33.33 MHz 时钟。 当我们将其乘以2倍时、没有合理的画面。 屏幕左侧有一些模糊的输出、但大部分屏幕都是模糊的黑色。

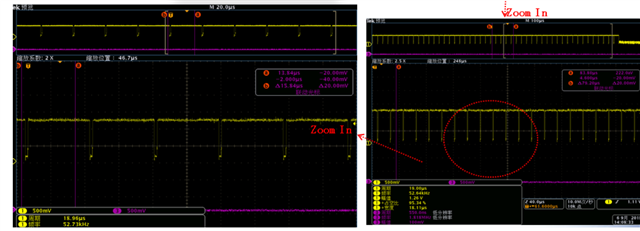

如果我将寄存器3c 中的位4设置为输出测试图形、则显示输出正常。 因此 REFCLK 可以。 DSI 输出正常。 芯片将无法正常工作。

水平分辨率为1024像素、在给定频率下、LVDS 接口每行输出1388像素。

为了使水平时序相等、我将 DSI 输出设置为83.333 MHz、并每行输出1735个像素(1024个有效)、因为(83.33/66.66)* 1388 = 1735

这将允许 sn65dsi83按照要求输出视频、但它不能。

当我通过 I2C 读回这些寄存器时、这些寄存器的内容如下(匹配工具推荐的内容):

00:35

01:38

02:49

03:53

04:44

05:20

06:20

07:20

08: 01.

09:01

0A: 84.

0b:01

0d:01

10:36

11:00

12:64

18: 78

19:05

1A:03

1b:00

20:00

21:04

24:58

25:02

28:21

29:00

2C:2C

2D:00

30:11

31:00

第34章:我是你的

36:17

第38章:我是你的

3A:A0

3c:00

E0:00

E1:00

E5:80