主题中讨论的其他器件: DP83869

工具与软件:

大家好、团队成员:

请帮助查看随附的 DP83869HM 原理图。

请注意:

1.我们使用 PHY 作为介质转换器

2.连接了具有 SFP 和铜缆接口原理图的 PHY。

3.我们有2个 PHY IC,原理图对于 PHY2是相同的,所以只连接了 PHY1原理图。

4.电源部分正在等待我将在接下来的线程中分享它。

e2e.ti.com/.../SCH_5F00_DP83869_5F00_TI.pdf

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好、团队成员:

请帮助查看随附的 DP83869HM 原理图。

请注意:

1.我们使用 PHY 作为介质转换器

2.连接了具有 SFP 和铜缆接口原理图的 PHY。

3.我们有2个 PHY IC,原理图对于 PHY2是相同的,所以只连接了 PHY1原理图。

4.电源部分正在等待我将在接下来的线程中分享它。

e2e.ti.com/.../SCH_5F00_DP83869_5F00_TI.pdf

尊敬的 Arijeet Saha:

为了审查原理图、您能否填写 设计审查清单并提交给我? 您可以在 DP83869产品页面-设计工具和仿真 。 收到已填写的清单后、最多需要5个工作日进行审核。

此致、

Alvaro

尊敬的 Alvaro:

我随附了更新后的原理图和检查清单文件、供您参考。 请查看并告知我们您的意见。

我们主要关注的是我们选择的磁性器件以及 IC 是否支持内部架构。

e2e.ti.com/.../MEDIA_5F00_CONVERTER_5F00_TI_5F00_REVIEW.pdfe2e.ti.com/.../DP83869_5F00_Schematic_5F00_Checklist.xlsx

尊敬的 Arijeet:

我将在检查清单中添加磁性注释。

我有关于铜线端链路检测的问题 是否还需要检测光学端? 反之亦然?[/QUOT]DP83869HM 具有独立的寄存器来检测铜缆链路和光纤链路。 《DP83869故障排除指南》 的3.2.1条光纤寄存器详细介绍了这些寄存器的行为。

此致、

Alvaro

尊敬的 Arijeet:

感谢您的耐心等待、请附上我的反馈。 下面的解释已在文件中提供、但我也想在此重申。

________________________________________________________________

我知道您的 PHY 不会进行 MDIO (寄存器)访问、并且您希望这款1000Mbps 介质转换器完全独立于硬件自举运行。 这是完全有可能的。

默认情况下:

在检查清单反馈中、我在 LED0连接上添加了一条注释以将其设置为高电平、从而强制实现光纤速度。

e2e.ti.com/.../Mistral_5F00_DP83869_5F00_Schematic_5F00_Checklist_5F00_TI-Feedback.xlsx

此致、

Alvaro

尊敬的 Alvaro:

感谢您发送编修。 我们将更新相同内容。

使用强制1000BASE-x 而不是自动协商有何具体原因?

寄存器 我们认为磁性材料 MPN 与 HX5012FNL 继续合作。 请分享您对此器件的观点吗?

寄存器 电源序列需要遵循数据表中共享的序列。 如果 VDDIO 在1V1和2V5之前斜升、该怎么办?

请您查看我们的电源部分(3电源配置)并对时序控制逻辑发表评论吗?

我们的一个卡上存在链路检测问题。 我已经提出了一个问题。 如果我们缺少任何故障排除步骤、请检查并提出建议。

尊敬的 Arijeet:

在光纤中、速度不是由自动协商决定的、我们实际上需要强制它。 根据我在实验室中使用不同板的经验、我一直都必须对光纤应用强制提高速度。 在 您发送的 E2E 链接中、我认为这就是您看到的问题。 如我的反馈中所述、可以在寄存器0xC00[12]中或通过更改 LED_0上的 strap 配置来禁用光纤自动协商。

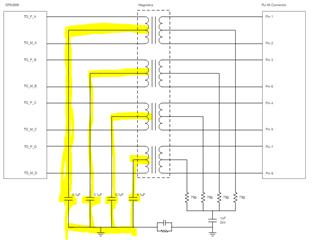

HX5012FNL 看起来不错。 我在检查清单中关于变压器中心抽头的评论仍适用于该器件。

VDDIO 可以在1v1和2v5之前斜升。 工程师 Hillman Lin 是我的同事。 我将与他协商,让他回答这个问题。

此致、

Alvaro

尊敬的 Alvaro:

A. 所有评论都将根据您的评论进行更新。

B. 寄存器 磁性元件:您能告诉我如何决定磁性元件的内部架构吗? HX5014具有不同的内部架构。 与 HX5008 (在参考设计中使用)相比、那么我们需要考虑哪些因素? HX5008在共模扼流圈之后提供中心抽头、而 HX5014在共模扼流圈之前提供中心抽头。 如果可以、则意味着由于空间限制、我要将磁性元件 MPN 更改为 HX5020FNL。

c. 还请提供帮助、分享您关于电源部分和我们设计中遵循的时序(逻辑)的评论。 由于空间限制、我们可能需要转换为电路板的2电源逻辑。

D. 我们期待更多的优化、因此、我们也不在我们的设计中使用 JTAG、允许 DNI:JTAG-TMS、CLK 线路元件。

E . 寄存器 在 E2E 主题中、我们尝试了强制协商、但仍然没有任何帮助。 我们还尝试了在 OPMODE 000中配置 PHY。 不过、我们仍然无法在铜缆侧或光纤侧看到任何链路。

当然可以、请仔细观看、并告诉我们各种可能性。

尊敬的 Arijeet:

A. 很好听到

B. 除了磁性规格(回波损耗、插入损耗、匝数比容差等)外、我还会检查变压器的中心抽头是否具有单独的连接、以便每个中心抽头都可以获得自己的0.1μF 电容器(请参阅图1)。 检查清单中提到了这一点。 通常、我们希望 CMC 位于变压器之后。

数据表中的图1 -磁性连接示例

c. 您在哪里提供了电源时序逻辑? 如果我错过了它,请原谅我,但我看不到它在清单。 您的电路板有哪些功率限制?

D. 是的、所有 JTAG 引脚都是可选的、如果不使用、则可以保持悬空。

e. 我将让我的同事继续处理 单独的 E2E 主题。

此致、

Alvaro

尊敬的 Alvaro:

对于空间 PCB 限制导致的设计更新、请分享您的宝贵意见

A. Pulse Electronics 提供的 HX5020NL、用于我们的应用。

b:采用2电源模式 我们将为所有电源轨使用 Switcher、并且所有电源轨都同时启用(此处不遵循定序)。

C.仅使用 JTAG-TDO 和 TDI、其余 JTAG 网络不连接。

d.禁用镜像模式且启用直通。

E.纤维保持在强制模式,铜在 Autoneg (如前所述)。