工具与软件:

您好、TI 团队。

我们在计算模块中使用 AM6254和 DP83867。

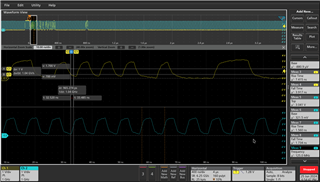

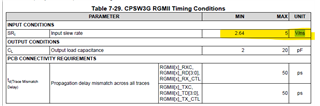

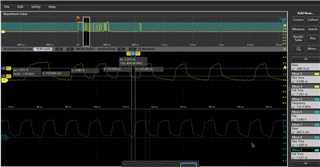

在这里、我们观察到 RGMII 接口中存在时序相关问题。 TXCLK 和 TXD0数据具有更长的上升和下降时间、无法实现所需的1ns 建立时间和保持时间。

请参阅随附的图。 建立时间约为322ps (在数据线路的 VIL 与时钟中心之间测得)。

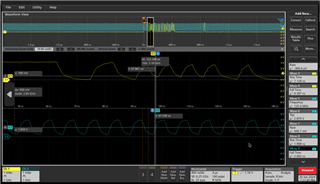

我们也有 EVM (E3A 版本)。 我们使用该电路板测量信号时发现了良好的信号。 我们可以在这里实现1.2nS 的设置和保持时间。

这里是否有任何与驱动器容量控制相关的内容? 在我们的设计和 EVM 板中、总体而言表现相似。

您能建议进一步的步骤来解决此问题吗?