主题中讨论的其他器件:TDA2

工具与软件:

尊敬的 PHY 团队:

祝您度过美好的一天! 我的客户遇到一个问题、请帮我回复:

硬件背景:使用 SOC:TDA2S +PHY 芯片:DP83TC813S;

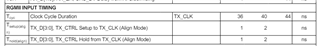

软件配置:SoC 侧 RGMII 接口(RX 和 TX 配置为对齐模式)、PHY:DP83TC813S (RX 配置为延迟模式、TX 配置为对齐模式);

问题:当计算机连接到光传输时、帧会丢失。

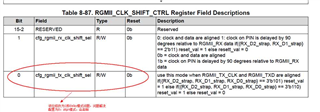

解决方法:通过修改 PHY 端的602寄存器位0 = 1来解决、如下所示:

他们有两个问题:

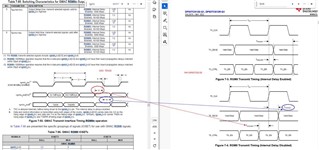

问题1:请帮助提供可与 PHY 侧(延迟)模式匹配的 SOC 侧(TDA2S)对齐模式的时序图;

问题2:在手动模式中、SOC 端默认为延迟模式、这取决于 SOC 是否为延迟模式、PHY 必须为对齐模式。 时序如下所示:

此致、

插孔