工具与软件:

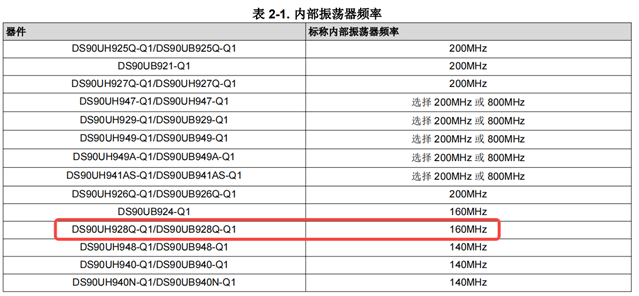

现在我们有一个项目想使用928输出图形图像、但在配置相关的寄存器928至 MCU 之后没有图像。 我们需要的显示参数如下:

![]()

我们为928通过 MCU 配置的寄存器列表 如下所示(根据 SNLA132);

#define PGIA 0X66//!<间接地址寄存器

#define PGID 0x67//!<间接数据寄存器

(0X010X06);

(0X02、0XF0);

(0X1c、0x03);

(PGIA、0x03);

(PGID、0x05);

(PGIA、0x07);

(PGID、0x56);

(PGIA、0x08);

(PGID、0x03);

(PGIA、0x09);

(PGID、0x1E);

(PGIA、0x04);

(PGID、0xE8);

(PGIA、0x05);

(PGID、0xD3);

(PGIA、0x06);

(PGID、0x20);

(PGIA、0x0C);

(PGID、0x48);

(PGIA、0x0D);

(PGID、0x09);

(PGIA、0x0A);

(PGID、0x06);

(PGIA、0x0B);

(PGID、0x01);

(PGIA、0x0E);

(PGID、0x03);

(0x65、0x04);

(0x39、0x02);

(0x64、0x41);

I2C 通信正常,配置后,模式在实际中不显示,测试 PLCK 仅超过27MHz , VS 仅为53Hz,但 HFP, HBP 和 HSW, VSW 波形与我们设置的参数相同,请帮助检查是否有我们遗漏的配置或任何建议。