Other Parts Discussed in Thread: TUSB8020B, TUSB7340

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

主题中讨论的其他器件:TUSB8020B、 TUSB7340

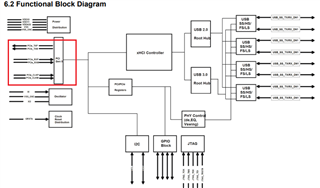

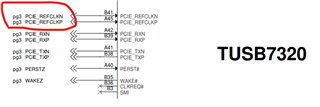

我浏览了 TUSB8020B IC 数据表和第25页(图7-3. 参考设计1)时、REFCLK 引脚会路由至连接器。

这里假设 PCIe 通信基于单独的时钟架构。

那么、为什么您仍然建立 REFCLK 连接、因为根兼容性和端点都将具有一个具有所需 ppm 容差的单独时钟。

我对为什么 REFCLK 连接仍然存在感到困惑。

如果您能加以详细说明会很好