Thread 中讨论的其他器件: TUSB4020BI

工具与软件:

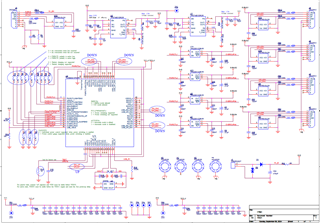

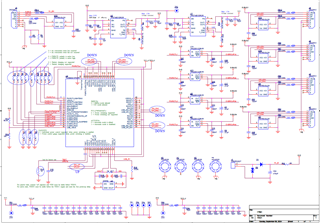

在 TUSB4041I 调试中、当下游端口未连接负载时、VBUS 没有电压。 经调查发现 PWRCTL1/2/3/4处于低电平(0.02V)。 外设配置与原理图中的设计一致。 测量后发现除 PWRCTL1/2/3/4之外所有引脚的电压电平均符合设计预期。 请帮助检查设计是否存在任何问题。 谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

在 TUSB4041I 调试中、当下游端口未连接负载时、VBUS 没有电压。 经调查发现 PWRCTL1/2/3/4处于低电平(0.02V)。 外设配置与原理图中的设计一致。 测量后发现除 PWRCTL1/2/3/4之外所有引脚的电压电平均符合设计预期。 请帮助检查设计是否存在任何问题。 谢谢!

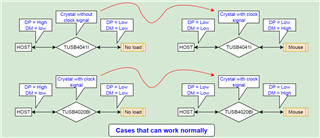

在正常工作情况下:

在空载运行过程中、TUSB4041I 的一些晶体会产生振动、而另一些晶体不会产生振动、并且所有晶体在带载条件下都会产生振动;

无论晶体是空载还是负载、TUSB4020BI 都会产生振动。

空载时、上行端口为(DP =高电平、DM =低电平)、下行端口为(DP =低电平、DM =低电平);

有负载时、上行端口为(DP =低电平、DM =低电平)、下行端口为(DP =低电平、DM =高电平)。

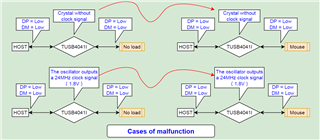

在发生故障的情况下:

无论空载还是负载、TUSB4041I 都不会振动。

无论负载如何、上行端口均为(DP =低电平、DM =低电平)、下行端口为(DP =低电平、DM=LOW)。

用晶体振荡器(1.8V)更换晶体仍然无法正常工作。

注:测试过程中使用了低速器件(鼠标)。