工具与软件:

大家好、团队成员:

我们正在开发一种应用、在该应用中、我们将 SN65DPHY440SS 用作具有2个数据通道和1个时钟通道的 MIPI CSI-2接口的转接驱动器。 我们目前正面临数据通道0未被正确"重新驱动"的问题。 使用示波器探测信号时、似乎转接驱动器未进入 Hs 模式、仅传输信号的低速边沿。

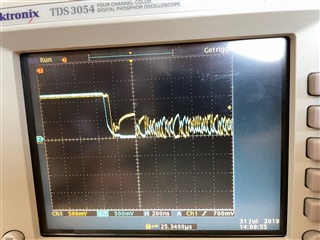

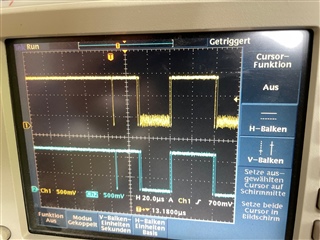

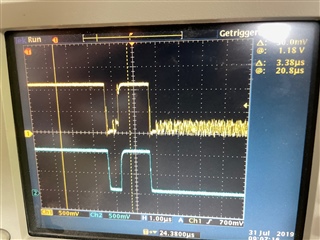

下图显示了 SN65DPHY440SS 的输入(黄色)和输出(蓝色)信号

您可以看到、HS 数据未传输、信号的其他部分也看起来不正确。 数据信号1和时钟信号看上去都正常。 我已经尝试启用仅 HS 模式、正如此论坛帖子: https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1345522/faq-sn75dphy440ss-is-it-okay-to-swap-the-polarity-and-lane-order 所建议的那样

不幸的是、这会产生相同的结果。

这种行为的原因可能是什么?

此致、

TIM