Other Parts Discussed in Thread: TLK6002

工具与软件:

您好!

我正在从定制的 FPGA 板将数据传输到 TLK6002板、并执行浅回送、然后将相同的数据发送回 FPGA 硼、在 FPGA 板中、有时不会发生时钟锁定。

但 TLK6002通道同步正常。

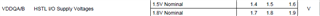

当我使用 HSTL 逻辑配置 TX 时钟、TX 数据、Rx 时钟和 Rx 数据时、会发生这种情况、但当我使用 LVCMOS Rx 时钟配置这些信号时、会正确锁定。

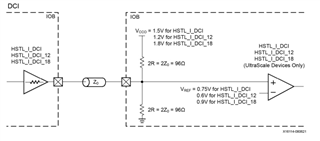

根据我的理解、LVCMOS 逻辑不需要端接电阻器、但在 HSTL 逻辑中、我们必须维护端接电阻器。

在上图中:输出是指 TLK6002生成的输出阻抗? 为此、我必须在 FPGA IP 中配置多少阻抗。

我必须提供多少输出阻抗。

谢谢、此致、

Mallikarjuna。