Other Parts Discussed in Thread: LMK1D2102

主题中讨论的其他器件:LMK1D2102

工具与软件:

您好!

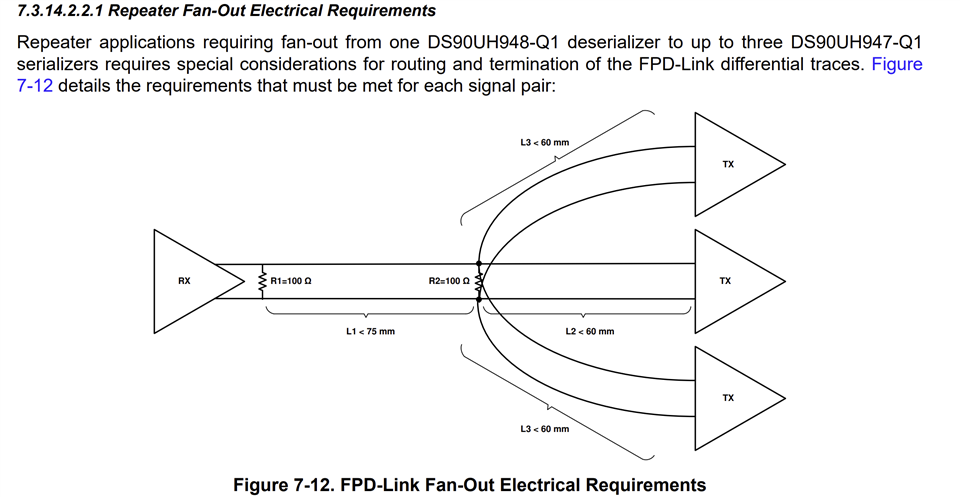

根据数据表中的图7-12第38页、我们正在设计应实现 HDCP 中继器模式的器件。 但在此类配置中与信号完整性问题有关。 为了检查这一点、我们从 图7-12中对设置/配置进行了简单仿真 、并且即使在 LVDS 速度较低(单对 LVDS 为100 - 200MHz)的情况下也得到了很差的结果。 同时点对点设置运行良好。 我们 在接收器侧使用了 DS90UH947。

问题是:如果我们在 DS90UH948和 DS90UH947之间插入扇出缓冲器、HDCP 中继器配置是否可以工作 ? LMK1D2102或类似器件。

此致、Aleksandr