工具与软件:

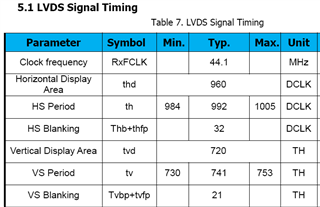

在这种情况下、 UB948解串器连接到 oLDI 2通道1920x720显示器、因此水平数据会拆分为偶数/奇数960像素。 显示屏具有以下参数:

问题:在 UB949串行器上设置测试图形发生器时、时钟频率和水平周期必须加倍? 然后、串行器会将数据拆分为偶数像素和奇数像素本身? 我可以请求 您为这种屏幕编写一个 patgen 测试脚本吗? UB949/UB948对使用双链路连接。 谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

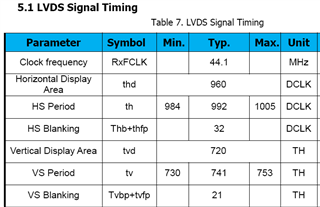

在这种情况下、 UB948解串器连接到 oLDI 2通道1920x720显示器、因此水平数据会拆分为偶数/奇数960像素。 显示屏具有以下参数:

问题:在 UB949串行器上设置测试图形发生器时、时钟频率和水平周期必须加倍? 然后、串行器会将数据拆分为偶数像素和奇数像素本身? 我可以请求 您为这种屏幕编写一个 patgen 测试脚本吗? UB949/UB948对使用双链路连接。 谢谢你。

您好、Philip:

根据显示规格、有时它会显示为"每端口"、其中使用双配置意味着横向加倍、因此 PCLK 也加倍。 垂直参数可能保持不变。

在这种情况下、我们可以研究以下规格:

总水平宽度=1984

总垂直宽度= 741

活动水平宽度= 1920

活动垂直宽度= 720

水平后沿= 20

垂直后沿= 8

水平同步宽度= 24

垂直同步宽度= 8

水平前沿= 20

垂直前沿= 5

PCLK 将由总垂直和水平参数决定、假设刷新率为60Hz、

PCLK = 88.21 MHz

我将通过参考 探索 FPD-Link III IVI 器件的内部测试图案生成特性(修订版 G)、为您提供所需的脚本、请给我一个工作日来执行相关工作。

此致!

Miguel

您好、Philip:

请参阅以下有关从 SER 启动 PATGEN 的适当寄存器写入的文件:

e2e.ti.com/.../_2300_-949-EVM-PatGen-Script-Example.py

如果您有任何问题、敬请告知。

此致!

Miguel