Other Parts Discussed in Thread: DS34LV87T, DS34LV86T

工具与软件:

您好、先生、

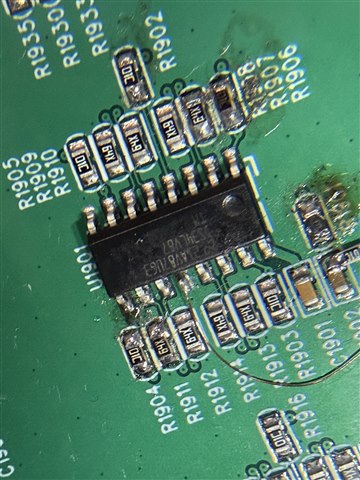

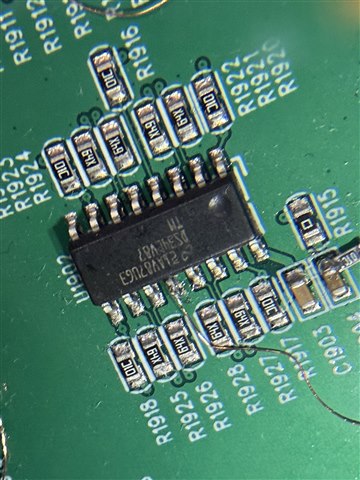

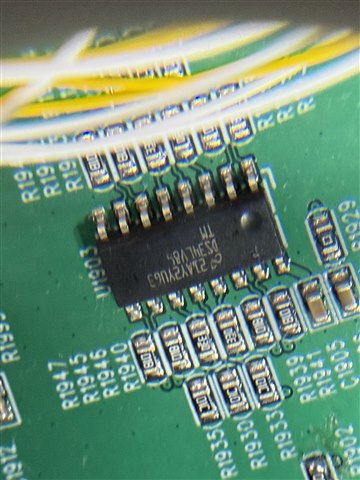

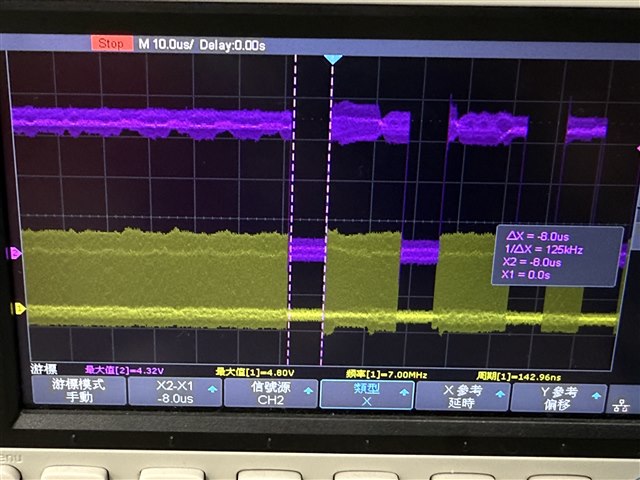

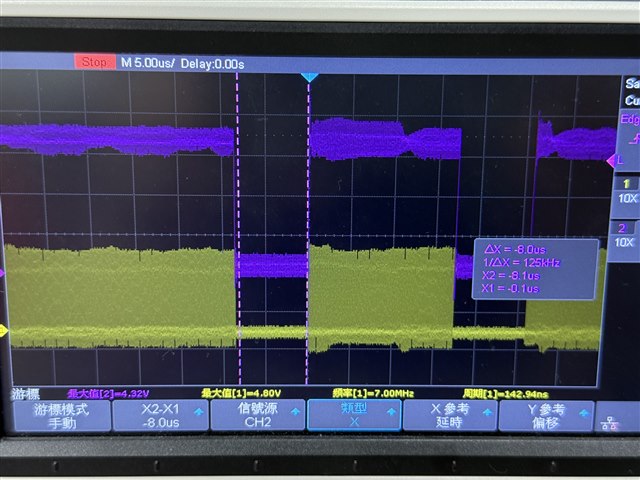

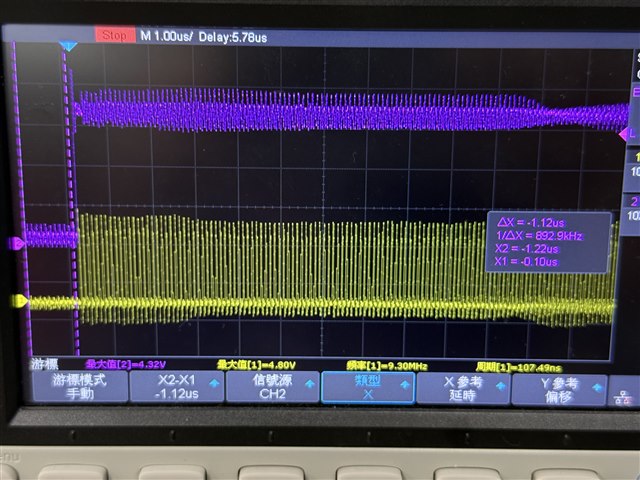

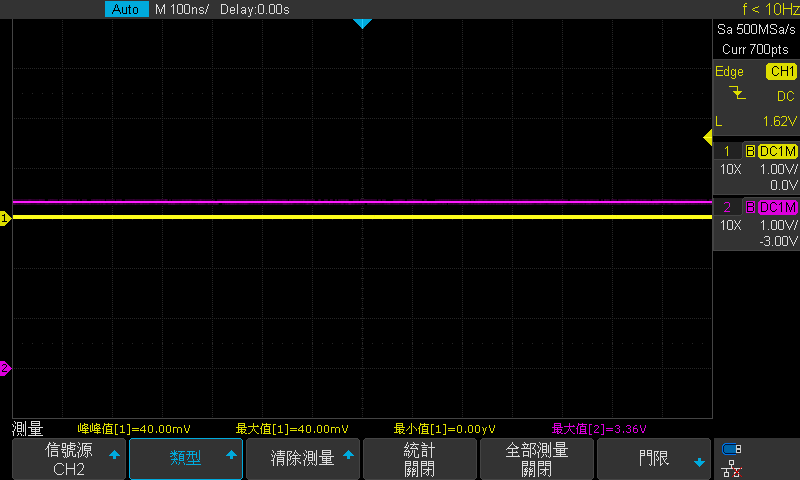

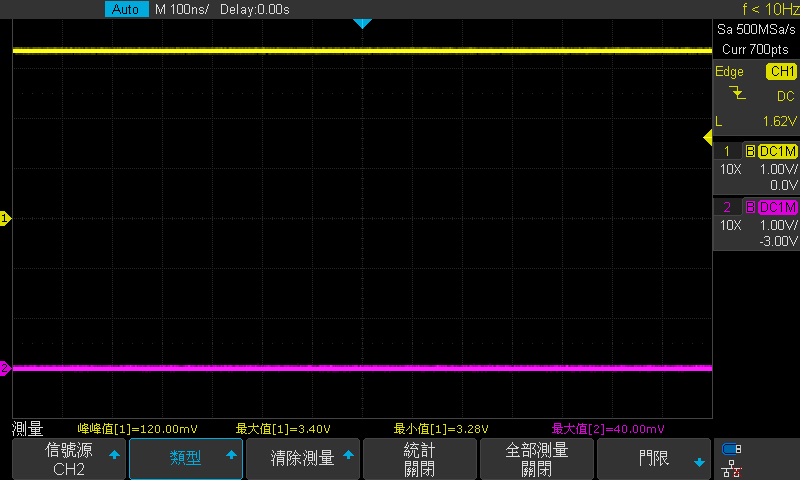

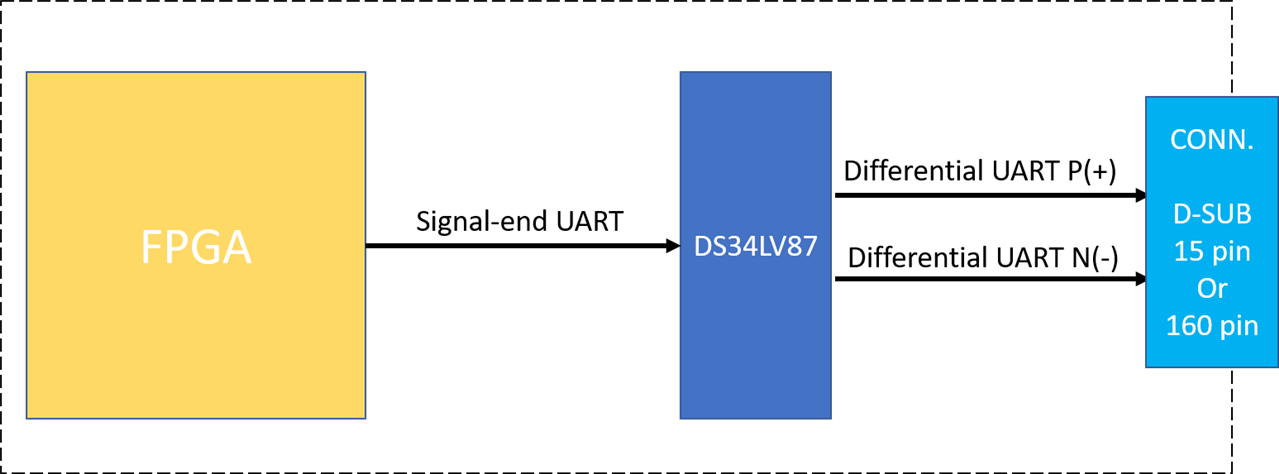

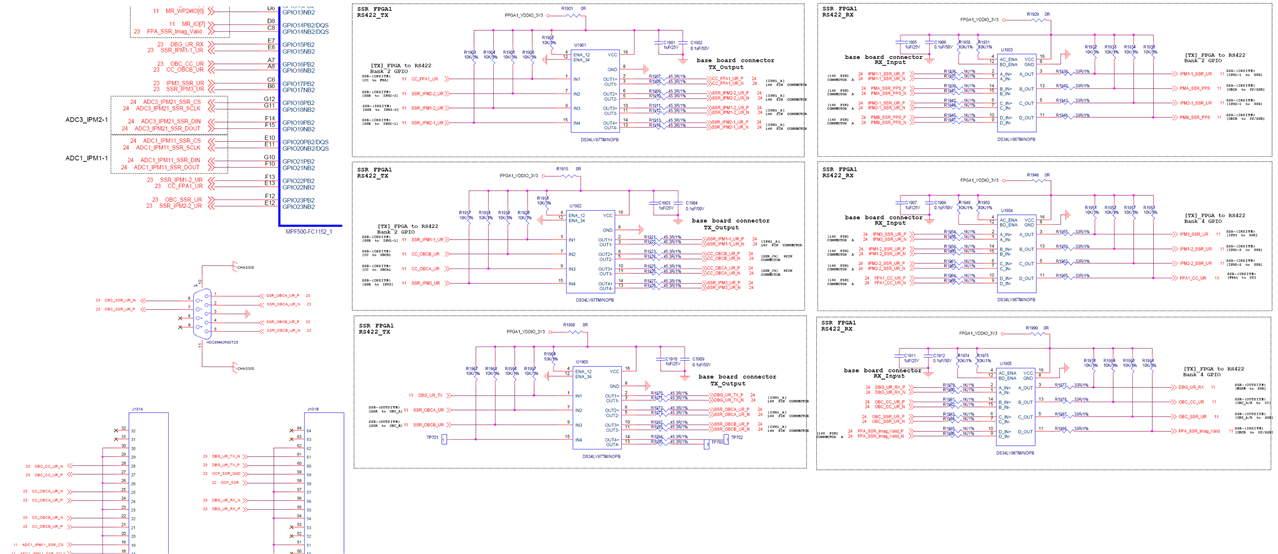

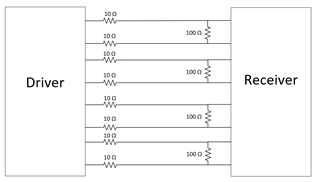

我们的系统使用三个 DS34LV87T 芯片将 UART 信号从单端转换为差分信号。 目前会遇到一个问题、即没有连接输入信号时、输出 P 表现出下图所示的波形。(仅上拉)

三个 IC 都遇到相同的问题。 我们已经尝试在输出端添加100欧姆的端接电阻、以防止其悬空、但这尚未解决该问题。

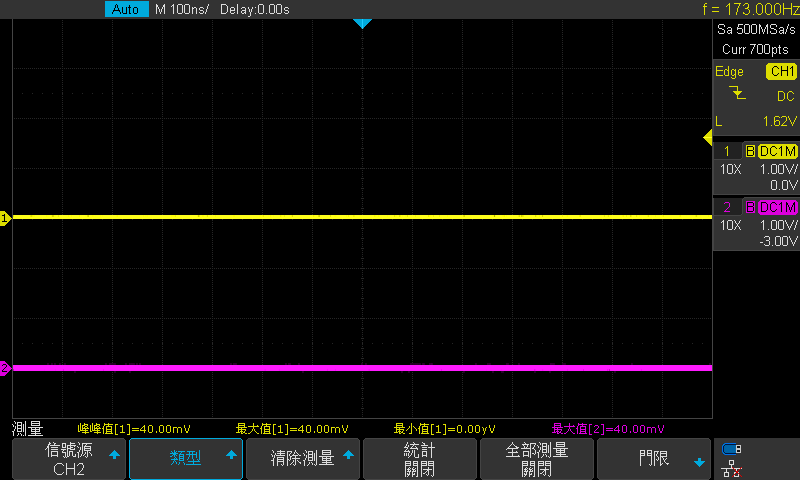

输出 N 未产生任何波形。

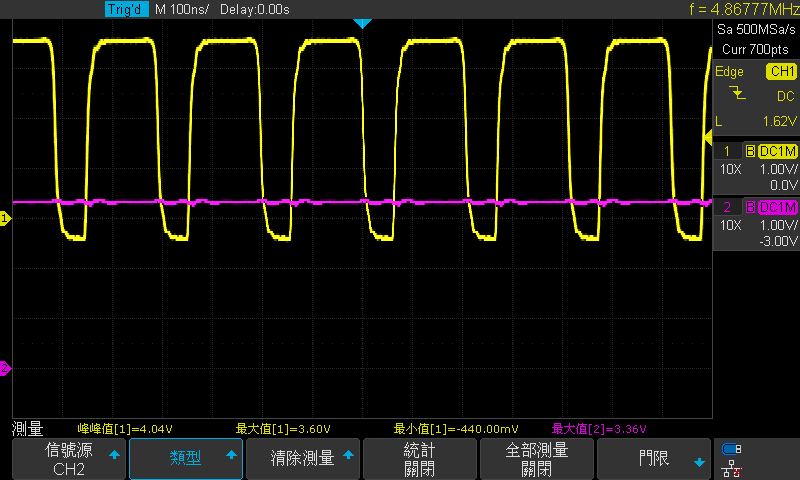

不过、奇怪的是、该状态仍然允许正常传输 UART 信号。