Other Parts Discussed in Thread: TLK10031

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1459524/tlk10031-tlk10031

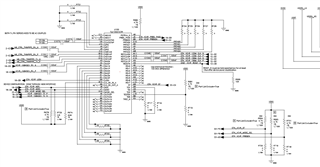

器件型号:TLK10031工具与软件:

您好!

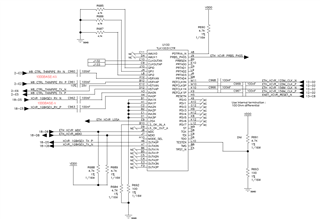

我在寻找 TLK10031的原理图实现方面的支持。 对于如何连接某些信号、我有一些问题。

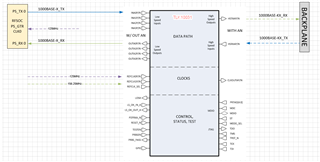

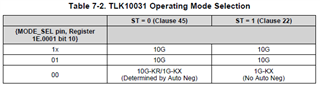

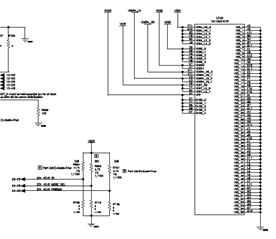

1.-如果我们计划将高速端口配置为1000Base-KX、将低速端口配置为1000Base-X、如何连接 MODE_SEL 和 ST 引脚

2.-如何连接 PRBSEN 信号?

3.-我需要将 PRTAD0..4引脚连接到特定地址、将它们全部接地还是保持未连接状态?

4.-边界扫描以外的其他应用是否需要 JTAG?

5.-是否需要通过 MDIO 进行编程/配置?

6.-您能否回顾一下原理图实现的准确性。