工具与软件:

嗨、团队:

作为从模式运行时、DP83825I 无法正确识别 TX。

但是、当我启用 RMII_TX_RMII 时 Clock_Shift、它可以正常工作。

我假设这是因为没有为 TX 提供保持或设置时间、对吗?

当此时启用该寄存器时、我也不知道哪个时间会发生时钟移位。

您能告诉我在数据表中的什么地方查看吗?

此致、

柳。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Vivaan:

是的、我明白。

我期待您尽快作出答复。

请告诉我们其他信息。

我在数据表的 P9上找到了以下陈述

RMII 从器件输出时序默认支持高达7.5ns 的设置时间。 对于7.5ns 至10.5ns、应编程寄存器0x0017.8 = 1、0x0042 = 0x0014 "

但是、找不到该寄存器。

您能不能也给我详细介绍一下这份声明的含义?

此致、

柳。

你好 Ryu、

是的、我明白了。

我期待您尽快回复。

感谢您的理解。

但是、找不到此寄存器

寄存器0x0017可在数据表寄存器映射中找到、但寄存器0x0042是供内部测试使用的保留寄存器、因此它不属于公共数据表的一部分。 不过、我们意识到该寄存器的一个功能有助于处理与 RMII 时序相关的裕度情况、因此添加了该注释。 如果您面临这种边缘情况、即使它不是数据表寄存器映射的一部分、也可以写入和使用此寄存器

此致!

Vivaan

尊敬的 Vivaan:

我不太理解这一点、那么让我直说吧。

我认为4ns 是所需的最短建立时间。

如果4ns 不可用、我想通过移位时钟可以确保4ns、这样就不会出现问题。

最大值7.5ns 是什么意思?

这是时钟移位的值吗?

如果仍然不够(7.5ns~10.5ns)、是否意味着可以将寄存器调整为工作?

如果可能、如果您可以在图表中显示这一点、则更容易理解。

此致、

柳。

你好 Ryu、

是的、所需的最短建立时间为4ns。

但是、支持的最长建立时间为7.5ns。

这意味着如果 测得的 引脚时间延迟在7.5ns 和10.5ns 之间 、您需要执行以下寄存器写入。 (编程寄存器0x0017.8 = 1、0x0042 = 0x0014)

这未考虑寄存器0x17的时钟移位 . 通过该寄存器启用的时钟移位发生在内部、因此无法在引脚本身上测量其影响。 这讨论的是 在引脚上测量的延时时间。 在引脚上测量到的延迟可能是由于布线延迟或 SoC 侧增加的内部延迟所致。 无论何种情况、此延迟都是指的延迟、而不是内部 PHY 延迟。

我希望这将使它更加清楚。

此致!

Vivaan

尊敬的 Vivaan:

抱歉。

我仍然不明白。

我认为、如果在引脚上测得的延迟是7.5ns 到10.5ns、那么通过时钟移位在内部移动4ns 将不会达到最小值4ns、也将无法识别。

我们讨论的是在何时可以为原始数据设置多少建立时间?

例如、如果数据传输完全没有延迟、并且设置时间为4ns 安全、那么到时钟移位时、我预计设置时间为8ns。

如果此数据延迟7.5ns、即使时钟发生移位、建立时间也将仅为0.5ns。

我的理解错了吗?

此致、

柳。

你好 Ryu、

我们在此应用中需要查看3种情况

我认为如果在该引脚上测得的延迟是7.5ns 到10.5ns、那么通过时钟移位在内部移动4ns 将不会达到最小值4ns、并且无法识别。

如您所述、在引脚上测得的延迟为7.5ns 至10.5ns、由于7.5ns > 4ns、它已经满足最小值4ns 的要求。 这些寄存器写入只是我们已找到的一种权变措施、可使器件在此边缘情况下正常运行。 不要从延迟的角度考虑这些寄存器的写入。

例如、如果数据传输完全没有延迟、并且设置时间为4ns、则当时钟发生移位时、我预计设置时间为8ns。

如果数据在没有延迟的情况下传输、建立时间将为0ns、因此无法满足4ns 要求。 增加内部延迟会导致其漂移4ns、这意味着总延迟/建立时间为4ns、符合要求、而不是8ns。

如果此数据延迟7.5ns、即使时钟发生移位、设置时间也将仅为0.5ns

我认为数据完全不会延迟。 延迟是根据数据和时钟之间的延迟来测量的。 此时钟是应延迟7.5ns 的时钟、从而产生7.5ns 的建立时间。

此致!

Vivaan

你好 Ryu、

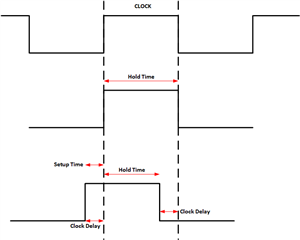

我制作了以下图示例说明了建立时间/保持时间。

中间数据信号是没有时钟移位的信号。 我们可以看到、由于上升沿与上面的时钟信号对齐。 由于这种对齐、我们可以看到没有建立时间。

底部数据信号向左移动、举例说明时钟延迟。 这与将时钟延迟到右侧是相同的。 在本例中、我们可以看到设置时间很短、这等于所增加的时钟延迟。 这就是为什么如果有4ns 的延迟、建立时间将为4ns 的原因。

这是否使它更加清晰?

此致!

Vivaan