Other Parts Discussed in Thread: LMH1297, LMH1229

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1469371/lmh1297-lmh1297

器件型号:LMH1297主题中讨论的其他器件: LMH1229

工具与软件:

您好!

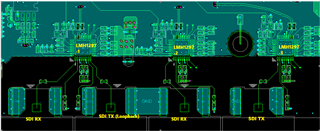

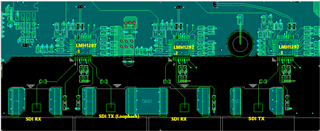

我在 E2E 论坛上看到此回复。 在我的应用中、我使用3个 LMH1297来实现12G-SDI 接收器和收发器。 但我遇到长电缆(50米)问题、它与下面的中所示的描述相关。

"请注意、启用 SDI_OUT 后、电缆长度预计会缩短10m 至15m。 SDI-out 会导致串扰并会缩短电缆长度。 "

LMH1297设置、

-芯片1:SDI_IO 为 EQ 模式。 SDI_OUT: 环回75 Ω 输出端口。 (Rx +环通 Tx)

-芯片2: SDI_IO 为 EQ 模式。 SDI_OUT: 未使用。 ( 仅限 Rx)

-芯片3: SDI_IO 为 CD 模式。 SDI_OUT:未使用。 ( 只适用于 TX)

我的问题是、当 Tx 启用@ 50米长的电缆时、12G-SDI Rx 无法正常工作。 A 下面中显示的 LL 测试结果在50米长电缆中进行了测试。

-测试1-1:当芯片1的 Tx 为时、芯片2可以正常接收12G-SDI 视频 "禁用"

-测试1-2: 当芯片1的 Tx 为时、芯片2无法接收12G-SDI 视频(解锁) "启用"

-测试2-1:当芯片 3的 Tx 为时、芯片2可以正常接收12G-SDI 视频 "禁用"

-测试2-2: 当芯片 3的 Tx 是时、芯片2无法接收12G-SDI 视频(解锁) "启用"

-测试 3-1: 当芯片1的 Tx 为时、芯片1可以正常接收12G-SDI 视频 "禁用"

-测试 3-2: 当芯片1的 Tx 为时、芯片2无法接收12G-SDI 视频(解锁) "启用"

Tx 似乎对 Rx 通道有一些影响、您可以帮助 确认此问题吗? 谢谢。

1. 启用 SDI_OUT 后、预计电缆长度会缩短10m 到15m。 <-正确吗?

2.如果上述描述正确、如果希望不降低电缆长度、则需要 Tx 和 Rx 之间的距离是什么?

3、 在我目前的布局中( SDI 连接器位置),有什么建议可以减少这一问题的影响? 示例:添加屏蔽。

谢谢。