主题中讨论的其他器件:DXP、 TS3USB221

工具与软件:

尊敬的接收者:

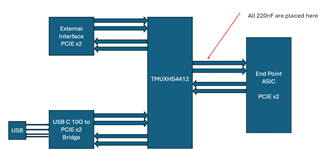

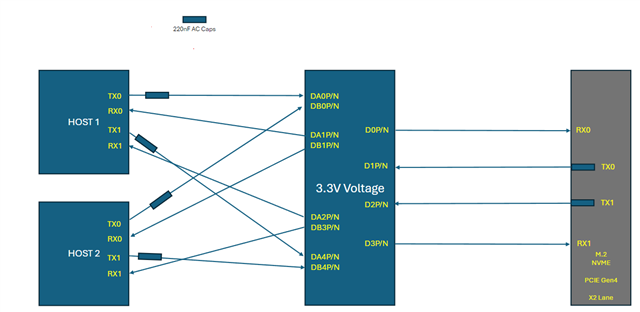

我们的设置如下所示

请帮我回答以下问题。

01.交流电容器的放置是否正确?

02.所有端口都支持85欧姆的阻抗?

请您尽快回写。 我们即将进入磁带输出阶段。

此致、

Sayeed Khan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的接收者:

我们的设置如下所示

请帮我回答以下问题。

01.交流电容器的放置是否正确?

02.所有端口都支持85欧姆的阻抗?

请您尽快回写。 我们即将进入磁带输出阶段。

此致、

Sayeed Khan

您好、Sayeed、

Unknown 说:01. 交流电容器放置是否正确?

此方框图很难判断交流电容器的放置位置。 通常、应在 PCIe 通道的 TX 线路上放置220nF 交流电容器。 我认为红线指向 RX 线、并且下游应该已经有220nF 的电容器、更靠近外部接口或 USB-C 桥。

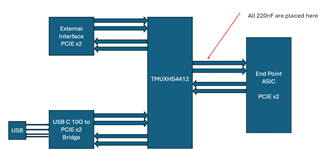

从端点 ASIC 流出的线路是我假设的 TX 线路、这些线路上应有220nF 电容、用于进行交流耦合。 下图很好地展示了建议如何放置交流电容器:

Unknown 说:02. 所有端口都支持85欧姆的阻抗?

是的、该器件应支持85 Ω 差分阻抗。

如果您有任何其他问题、敬请告知。

谢谢!

Ryan

尊敬的 Ryan:

感谢您尽早回复。

在方框图中、我们有两个到单个端点的根选项

1.外部 PCIe x2 (CFX)。 我们之前的设计尚未在这些线路上使用任何交流电容器。

2. USB 10G 到 PCIe x2 (板载)、此处我们需要具有 TX 交流电容器以及 RX 交流电容器。

目前、我已将所有交流电容放置在 TMUXHS 的 COM 侧、即端口 DXP/N 请告诉我,如果这种做法应该是好的??

此致、

Sayeed Khan

尊敬的 Ryan:

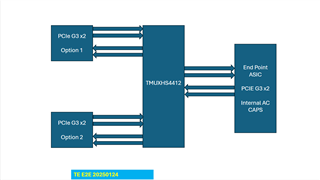

我更新了方框图

请注意

接下来、端点 ASIC 应是设备、方案1和2分别是主机1和主机2。

主机1:外部

主机器件2和器件位于同一 PCB 上。

1.当设备直接连接到 host1时,我们没有在设备 TX 上提供交流电容,因为它在 TX 通道上有内部交流电容,因为设备 RX 依赖于 host1交流电容。

2. 在本例中、由于主机2输入与器件位于同一 PCB 上、因此我们是否只能放置到主机2个 TX 通道?

3.关于 CMV,请您详细说明一下我需要检查什么参数主机2准确理解和实现.

谢谢!

Sayeed Khan

1. 当设备直接连接到 host1时、我们尚未在设备 TX 上提供交流电容器、因为设备 RX 上具有内部交流电容器、而设备 RX 依赖于 host1交流电容器。

明白了、如果 host1 tx 交流电容器和器件 tx 电容器都是220nF、那么我认为这应该是可以的。

2. 在本例中、由于主机2输入与器件位于同一 PCB 上、因此我们是否只能放置主机2个 TX 通道?[/QUOT]对于 host2到器件以及从器件到 host2、TX 线路上需要220nF 电容器。

host1或 host2通常不需要 Rx 电容器(330nF)。 对于两种情况、您只能在 TX 线路上设置220nF 的电容。 即使这些器件位于同一块板上、主机和器件的 TX 线路上也应该有电容。

[/quote]3. 关于 CMV、请您详细说明我需要检查主机2的哪些参数才能准确理解和实现。[/QUOT]需要确保的主要是您使用的信号的共模电压由多路复用器提供支持:

根据提供给多路复用器的电源电压、只要 VCM 处于数据表建议的范围内、信号就应该处于可接受的多路复用范围内。

如果这些信号不在可接受的范围内、则需要使用外部电阻器对其进行偏置:

如果您有任何其他问题、敬请告知。

谢谢!

Ryan

尊敬的 Ryan:

1.您是否有任何参考资料供我们分享给 CMV 的理解。 如果符合 PCIe 基本规范3.0和4.0、它是否需要 PCIe 第3代和第4代主机/终端?

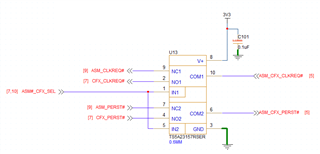

2.请查看以下参考资料,了解我们的2Host 1设备配置的完整实施

3.在 PCIe 第4代符合 TMUXHS4412标准中、他们是否使用了 CMV 偏置。

4.请分享 PCIe 第4代实施的任何参考/工作示例。 我们的董事会空间非常紧张,我完全陷入了 CMV 的困境。

我对你在这方面的帮助表示诚挚的问候。

此致、

Sayeed Khan

您好、Sayeed、

1. 您是否有任何参考资料供我们分享、以促进 CMV 的理解。 如果符合 PCIe 基本规范3.0和4.0、PCIe 第3代和第4代主机/终端是否需要该规范?[/QUOT]只要 PCIe 第3代和第4代的电压电平在数据表中列出的电平范围内、我认为只要多路复用器在 Vcc = 3.3V 下使用、就不需要担心偏置。 此器件的 PCIe 等级为3级和4级。

此常见问题解答为耦合和 VCM 提供了更好的解释: https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1342811/faq-tmuxhs4212-when-and-how-to-ac-coupling-the-passive-mux?tisearch=e2e-sitesearch&keymatch=tmuxhs4412#

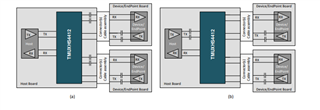

2. 请查看以下有关我们的2Host 1器件配置完整实施的参考资料我认为我认为此实施不会有任何问题

3. 在 PCIe 第4代与 TMUXHS4412合规性中、他们是否使用了 CMV 偏置??[/QUOT]本文档报告了我们的 PCIe 第4代合规性测试过程。 它应该提及或指示是否需要任何 CMV 偏置: https://www.ti.com/lit/ug/slat159/slat159.pdf

[/quote][/quote]4. 请分享 PCIe Gen4实现的任何参考/工作示例。 我们有一个非常紧张的房地产在我们的董事会,我完全陷入 CMV 的困境。[/报价]该报告应显示我们用于测试的电路板。 如果您愿意、我可以将电路板的设计文件发送给您查看。

谢谢!

Ryan

您好、Sayeed、

请接受我的 E2E 朋友申请、我会将这些文件交给您。

[报价 userid="639479" url="~/support/interface-group/interface/f/interface-forum/1465332/tmuxhs4412-use-of-ac-caps-impedance-control-for-pcie-g4/5631574 #5631574"]2.我已经使用了以下针对 CLKREQ 和 PEREST MUX 的实现。

我没说我 以前使用过这个开关。 从我能够知道的角度来看、我认为这个设置正确、是的。

我还想为2:1多路复用推荐一个器件:TS3USB221。不过、如果这个开关在电压和带宽方面适合您的话、我相信会更合适的。

谢谢!

Ryan

尊敬的 Ryan:

1.请查看我们的最终客户就此发表的意见,如果这些意见与您对 VCM 的意见一致,请告知我们。

2.感谢您分享朋友的请求。 请分享上述设计文件。

3.我的 host1是 PCIe 边缘指、host 2是板载芯片。 我刚刚在 YouTube 上从 TI 观看了一份 PCIe 指南、其中 CEM/边缘手指为85E、同一 PCB 主机为100E。 我是否以不同的方式连接它们/两台主机均使用85E。

谢谢!

Sayeed Khan

您好、Sayeed、

1. 请查找我们的终端客户就此发表的意见、如果这些意见与您对 VCM 的意见一致、请告知我们。

对我来说很有意义、我对它没有问题。

2. 感谢您分享朋友的请求。 请分享上述设计文件。

过 E2E PM 进行响应。

3. 我的 host1是 PCIe Edge Finger、host 2为板载芯片。 我刚刚在 YouTube 上从 TI 观看了一份 PCIe 指南、其中 CEM/边缘手指为85E、同一 PCB 主机为100E。 我是否以不同的方式连接它们/两台主机都使用85E。

最好在整个系统中具有相同的阻抗、这一个最接近符合 PCIe 差分阻抗规范的范围。 在布线或多路复用器中的不同阻抗之间切换只会导致信号反射。

如果您有任何其他问题、敬请告知。

谢谢!

Ryan

尊敬的 Ryan:

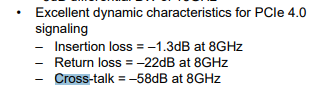

我需要担心下面的备注吗?

我可以使用整个多路复用器并具有完整吞吐量、对吧?

谢谢!

Sayeed Khan

尊敬的 Ryan:

对于 USB3.2 10G x2通道、我们只需将差分对内延迟匹配到<5mil 对吗? 差分对间延迟差不是必需的、对吧?

2. PCIe x2同样的准则?

3. TMUXHS4412 RSVD42,我左悬空,是好吗?

4.根据 DS 7.4、建议在持续供电以及充足的电容器后将 PD 拉低。 我已通过10K 硬连接至 GND。 EVM 此外、没有此类配置??

此致、

Sayeed Khan

您好、Sayeed、

对于 USB3.2 10G x2通道、我们只需将差分对内延迟匹配到<5mil 对吗? 差分对间延迟差不是必需的、对吧?

2. PCIe x2同样的准则?

[报价]正确、两种差分对内延迟差的建议值均小于5mil。 因此不需要线对间延迟差。

[/quote][/quote]3. TMUXHS4412 RSVD42、我保持悬空、是否正常?[/QUOT]应通过一个4.7K Ω 电阻下拉至接地。 它不能保持悬空。

[/quote]4. 根据 DS 7.4、建议在持续供电并配置充足的电容器后将 PD 拉低。 我已通过10K 硬连接至 GND。 EVM 此外、没有这样的配置?[/QUOT]如果可能、我建议仅在 VCC 稳定时驱动 PD 引脚拉至低电平、而不是将其永久下拉。

谢谢!

Ryan

您好、Sayeed、

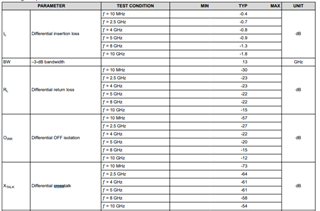

您能给我提供 PCIe 第3代和第4代的 IL、RL 和串扰规范吗? 我无法从数据表中解码此内容。

我相信首页中包含此方面的一些规格以及一些基于频率的参数:

除此之外、我认为我们没有任何其他专门针对第3代的规格。

谢谢!

Ryan