主题中讨论的其他器件:ISOW7741、

工具与软件:

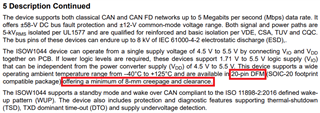

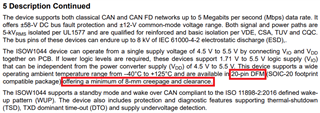

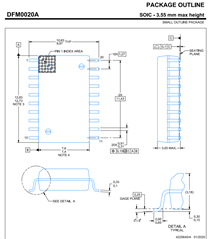

组件" ISOW1044DFMR "使用" DFM0020A "封装、根据数据表、此封装提供 最小爬电距离和间隙为8mm . 然而、在检查焊盘图案 尺寸时、间隙似乎实际上是存在的 小于8.00毫米、 即7.60毫米 . 请协助我们提供 土地布局 建议 包括定义的爬电距离和间隙(最小值8.00mm) 并提供相关指导。 随附的卡扣、便于您参考。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

组件" ISOW1044DFMR "使用" DFM0020A "封装、根据数据表、此封装提供 最小爬电距离和间隙为8mm . 然而、在检查焊盘图案 尺寸时、间隙似乎实际上是存在的 小于8.00毫米、 即7.60毫米 . 请协助我们提供 土地布局 建议 包括定义的爬电距离和间隙(最小值8.00mm) 并提供相关指导。 随附的卡扣、便于您参考。

尊敬的 Anand:

感谢您的联系。 请在下面找到我的意见。

尊敬的 Varun:

感谢您的及时响应、

根据您的响应、我可以了解数据表中8.00mm 的额定最小爬电距离/间隙与封装级别有关、不适用于焊盘图案。

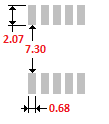

我们利用独特的焊盘图案计算器工具来确定焊盘尺寸和间距。 根据其输出、电容 c 相邻 焊盘之间的学习距离为7.30mm (请参阅随附的卡扣)、而数据表建议的间隙为7.60mm。

您能否澄清一下、是否需要遵守数据表中的建议间距才能保持高压/隔离的爬电距离和间隙、或 我们能否改用计算值?

出于好奇心、我注意到针对某些器件提出了两项不同的焊盘图案建议、其中一项遵循 IPC7351标准、而另一项则采用 HV/隔离选项。 我们的组件是否具有类似的模式?