Other Parts Discussed in Thread: ISO1540

工具/软件:

您好:

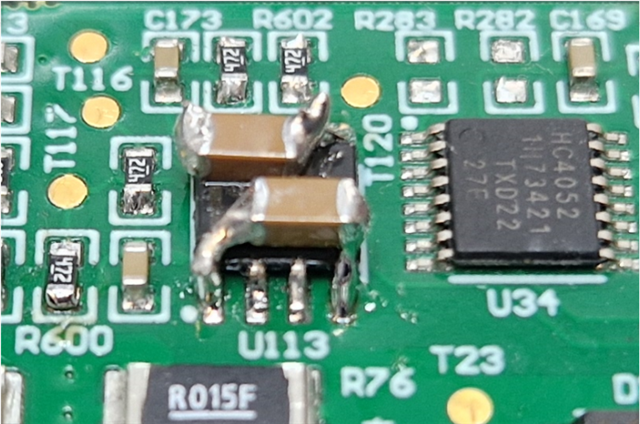

在设计中、我使用 ISO1540 芯片作为电压转换器。 是什么

- SIDE1 直接连接到 MCU

- Side2 连接到 74HC4052 多路复用器、使我能够在通信接口之间切换。 请参阅下面的原理图。

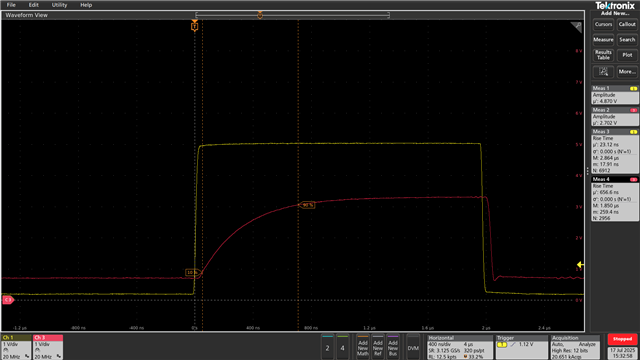

我注意到信号有问题

- 当 MCU 在 1 侧引脚 2 上生成信号时、ISO1540 似乎会使波形失真、并将此失真传播到 2 侧。

红色信号 1 侧引脚 2 (MCU); 2 侧引脚 7 上的黄色信号;

但是、如果将引脚 2 抬起、信号似乎正常

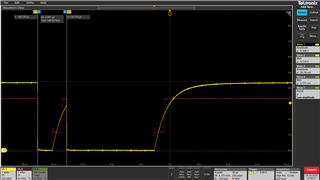

- 另一种情况是施加在 2 侧引脚 6 信号、然后在 1 侧引脚 3 失真。 慢速上升时间。 请参阅 下面的波形:

红色信号 1 侧引脚 3; 黄色信号 2 侧引脚 6;

我们非常感谢任何见解建议或类似的经验。