主题中讨论的其他器件:ISOW7842

在大规模生产中,我的客户遇到了 ISOW7842的故障。 ISOW 变为第二(ISO)端的短电流。

您能否修改计划并建议解决问题的方法?

附件中提供了技术详细信息:

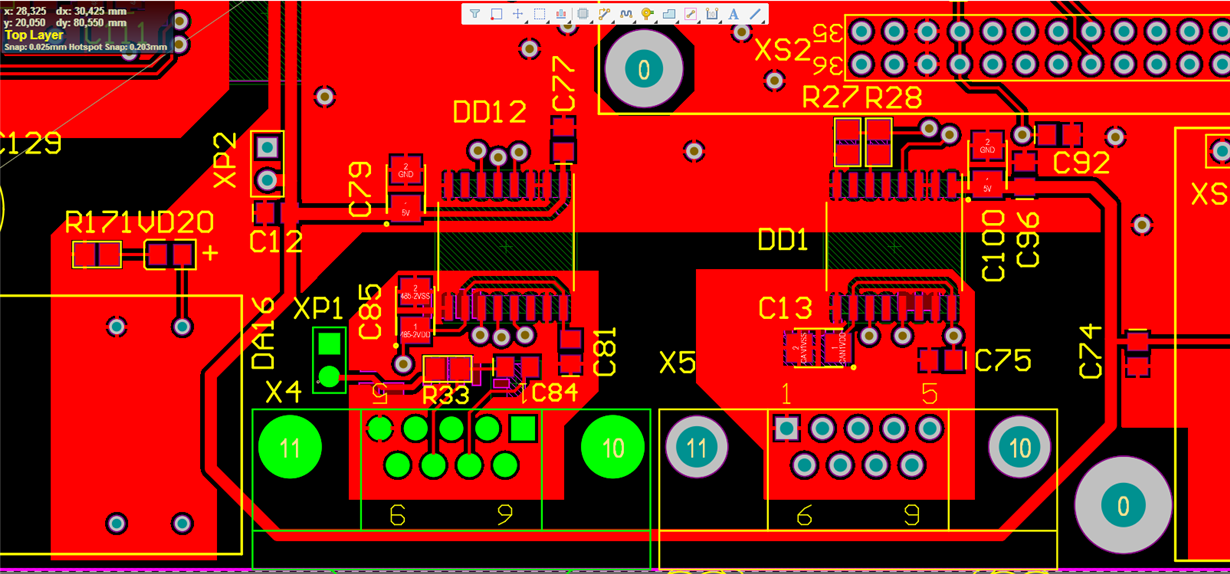

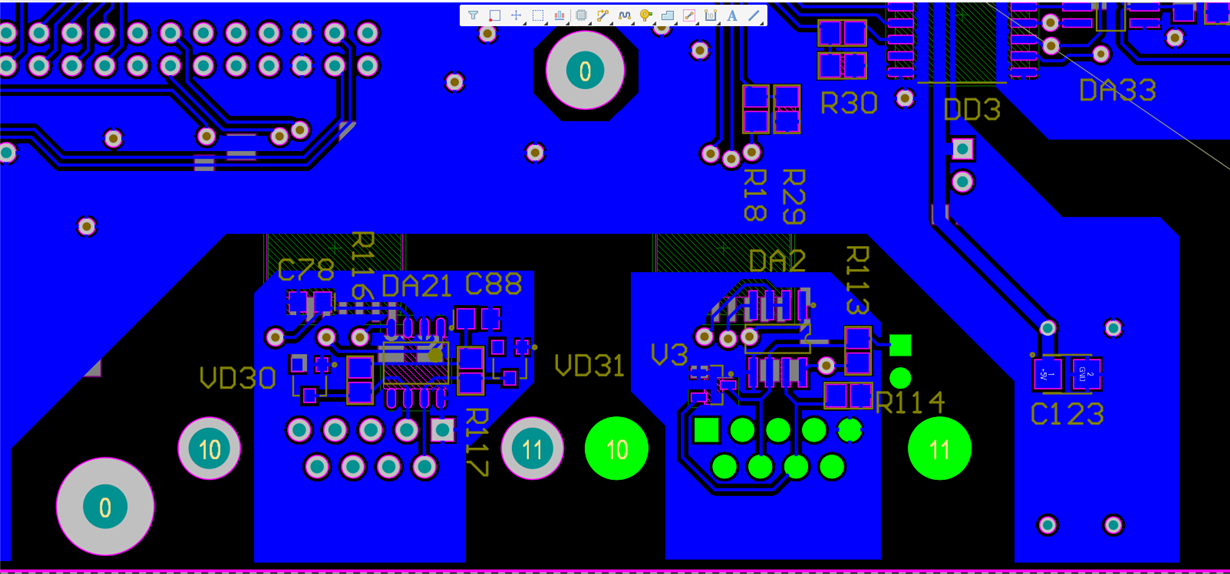

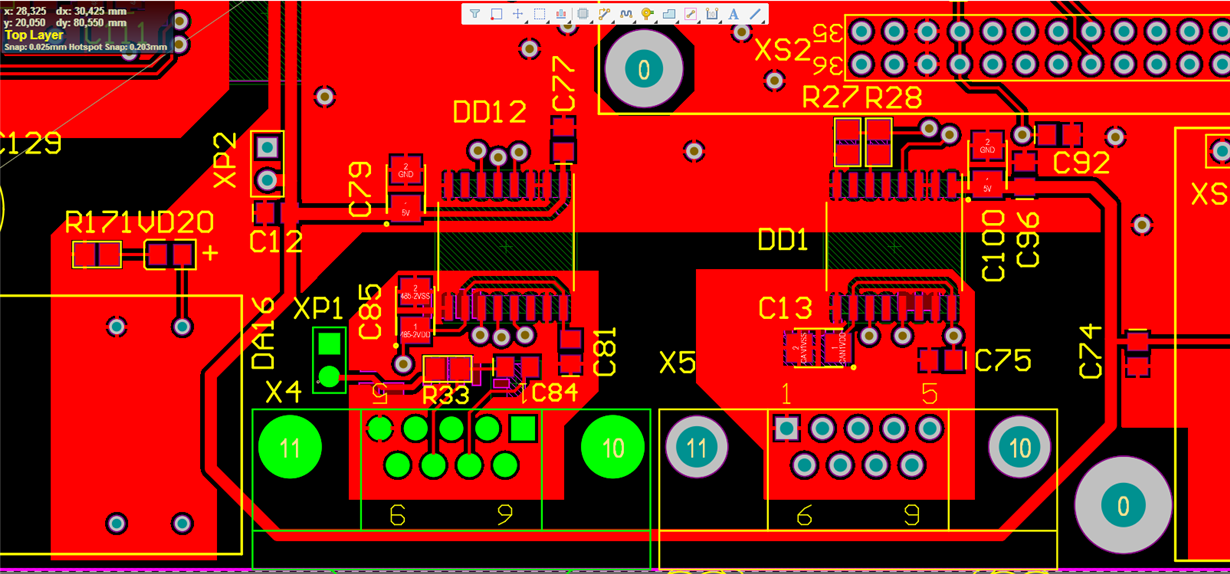

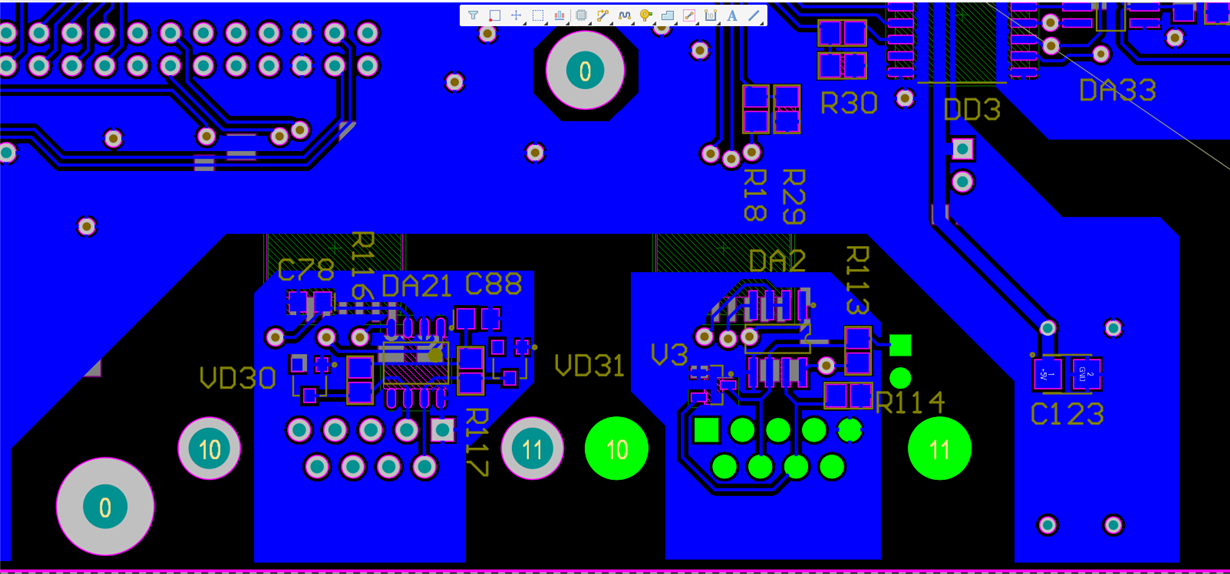

- TOP.png 和 BOT.png–是 PCB

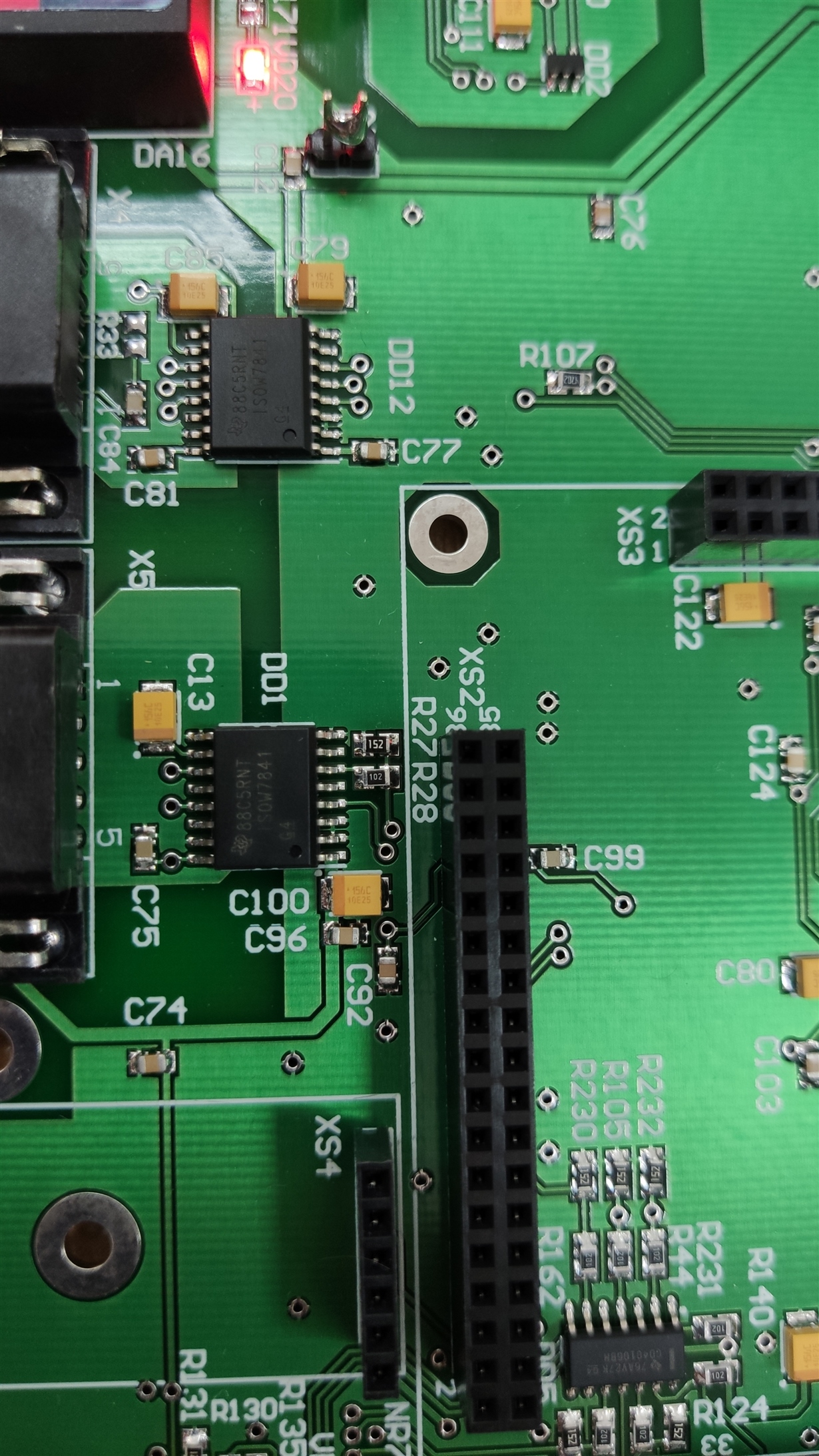

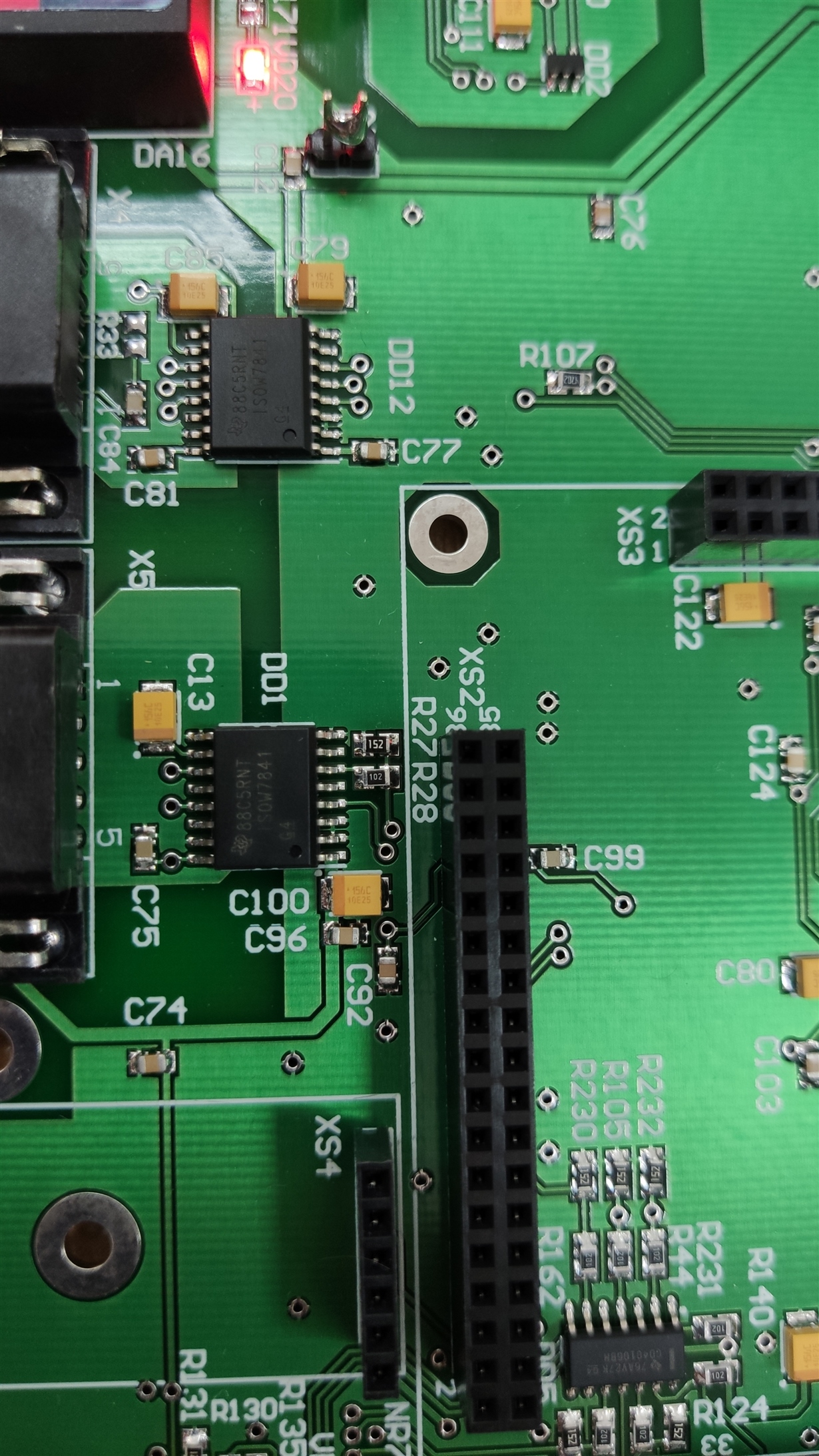

- img 20190903……jpg–board’s photo

- BldcPmsm.pdf -原理图

- e2e.ti.com/.../BldcPmsm.pdf

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在大规模生产中,我的客户遇到了 ISOW7842的故障。 ISOW 变为第二(ISO)端的短电流。

您能否修改计划并建议解决问题的方法?

附件中提供了技术详细信息:

尊敬的安德烈:

感谢您提供 PCB 图像和原理图。 Viso 引脚上的预期负载是多少? 每个系统中的同一单元(DD1、DD12、DD3)是否出现故障? 短路条件下的电压电平是多少?

我将等待你对上述初步问题的答复。

感谢你能抽出时间、

Manuel Chavez

尊敬的安德烈:

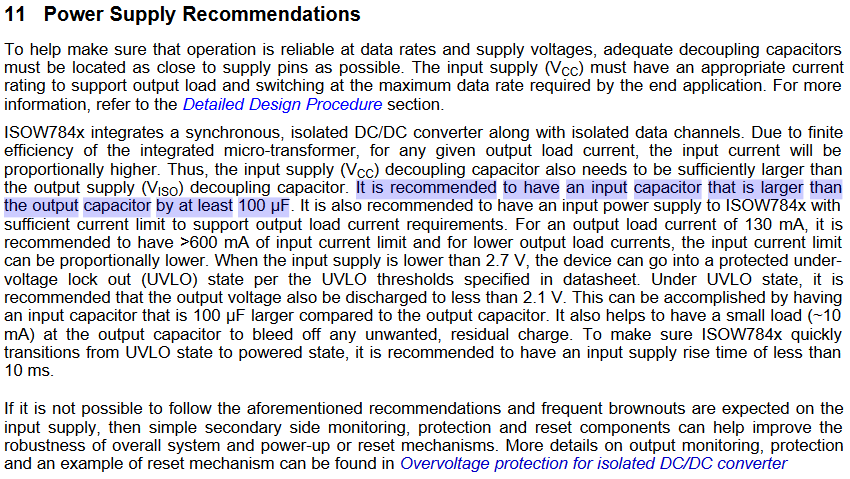

如 Manuel 提到的、解决这个问题的最佳方法是使 VCC 引脚上的总电容至少比 VISO 引脚上的总电容大100µF μ F。 您可以向客户推荐吗?

此外、我发现 VCC 和 VISO 上的去耦电容器放置存在问题。 该器件要求将所有电容器放置在与器件相同的一侧、而不应放置在 PCB 的另一侧。 同样重要的是、应将最小值的去耦电容器放置在最靠近器件引脚的位置。 有关电容器的放置、请参阅 EVM 的以下 PCB 布局。

如果您有任何疑问、请告知我们、谢谢。

此致、

Koteshwar Rao