Other Parts Discussed in Thread: SN6505B, SN6501

主题中讨论的其他器件: SN6501

是否可以并联两个 SN6505B 器件(一个在另一个器件的顶部)? 它们将与相同的 CLK 同步。 我们希望这样做、因为电流限制有时会生效。

谢谢、

Pablo

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Pablo、

欢迎访问 TI E2E 论坛!

您是否打算询问两个基于 SN6505B 的电源解决方案的输出是否可以连接在一起以增加功率? 或者、您是要问两个 SN6505B 器件是否可以并联到单个变压器以增加输入电流支持?

这两个问题的答案都不是。 这些器件没有任何功能允许它们并行连接、而外部时钟选项仅用于帮助客户将开关频率选择为其感兴趣的值、以帮助他们更好地管理发射。 谢谢。

此致、

Koteshwar Rao

我不太确定 你给我的两个选项问题之间有什么区别。 第二个问题似乎更接近我要做的事情。 有两个 SN6505B 器件、我想将器件1的 D1连接到器件2的 D1、将器件1的 D2连接到器件2的 D2。 D1和 D2都连接到变压器。

如果答案是否定的、那么我能否使用单个 SN6505B 来驱动外部 FET (D1连接到 FET1的栅极、D2连接到 FET2的栅极)、或者是否有其他方法来增加功率?

您好、Pablo、

正如 Koteshwar 提到的、不建议连接两个 SN6505 (或 SN6501)器件的 D1和 D2引脚、因为它们不能用于在多个器件之间分配电流负载。 开关特性的零件间差异可能会导致并联连接的任何两个器件损坏。

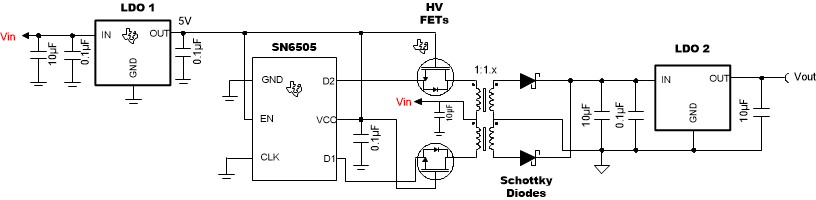

可以包含如下所示的外部 FET 以提高隔离式电源的功率能力、但该解决方案会增加初级侧的电压容量、而不是灌电流能力:

对于上述用于升压电流的解决方案、Vin 需要大于 Vout、变压器需要具有小于1的匝数比(降压变压器)。 此解决方案需要提供的最大负载电流是多少?

谢谢、

Manuel Chavez

您好、Manuel、

我们将 SN6505连接到可低至2.9V 的电池组、您的原理图中 LDO 2之后的输出电压需要保持在3.1V。

当输入电压低于输出电压时、是否有办法提高输出电压下的 Iout 电流?

如果我们可以在输入电压为2.9V 时从现有设计中获得更多150mA 的电流,我们就可以在输出电压侧进行操作。 我们的现有设计与您的原理图完全一致、只需将 LDO1替换为4.2V 电池组、然后在没有 HV FET 的情况下将 D1和 D2直接连接到变压器即可。 LDO 2输出3.1V。

谢谢、

Pablo

您好、Pablo、

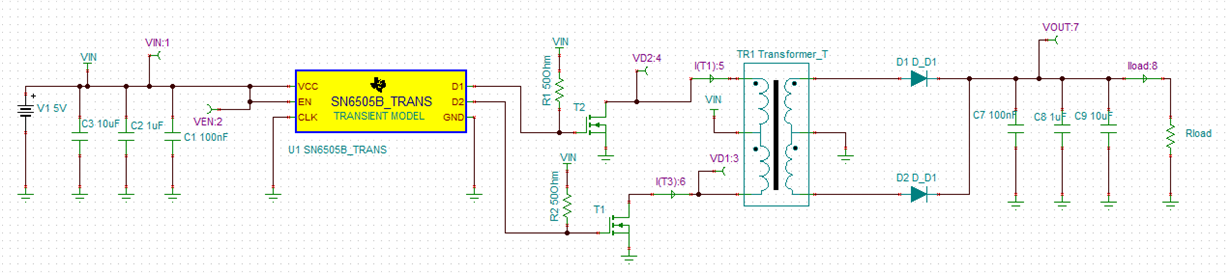

我们考虑使用 SN6505驱动>1A 的拓扑如下所示:

V1可在3V 电压下工作、但外部 N 沟道 FET 的 Vgth 需要远低于此值、并且能够吸收>1A 的电流。 需要多大的电流尚不清楚、但 SSM3K329R 等 FET 应该可以正常工作。

该设计在权衡后发现、SN6505的某些特性将在外部 FET 上丢失、例如电流限制和热关断。

请告诉我、如果这是您需要考虑的解决方案、否则隔离负载可在两个独立的 SN6505电源电路之间进行分配。

谢谢、祝您度过愉快的周末、

Manuel Chavez

您好、Pablo、

不用客气! 为了澄清这一点、您使用两个并联的 SN6505B 构建的配置是否共享接地连接、但隔离式电源轨是独立的?

此原理图中的 SS24T3G 二极管将阻止 SN6505和变压器的推挽操作、如以下文章中所述。 如果环境温度超过~85dC、当最大反向泄漏电流大幅增加时、这些二极管和使用的肖特基二极管也会对性能产生负面影响、并可能导致电源崩溃、这与 此 E2E 主题中提到的情况类似。

这些二极管如何降低 EMI? 这是我不熟悉的一种技术、我想进一步了解。

谢谢、

Manuel Chavez

注意:此帖子已更新以提高准确性

您好、Manuel、

我们正在考虑的配置也使用相同的电源轨。 就像在现有 SN6505B 上连接另一个 SN6505B。

感谢您提供有关二极管温度的提示。

现在、关于二极管如何降低 EMI ... 我不知道变压器线圈是否存在这种情况、但当 FET 打开时、 初级线圈的电压将反向、该初级线圈电压将添加到 V+电源电压、因此 FET VDS 电压将是电源加上初级线圈的反向电压 (电源2 * V+的两倍最大值)。 这意味着当 FET 关闭时电流更大。 另一方面、如果我们将一个二极管与初级线圈并联、初级线圈的反向电压将漏极到电源的 V+、因此 FET VDS 最大电压将是电源电压加上二极管的正向电压 (电源加0.6V)。 FET VDS 不大、因此它将降低 FET 开关时产生的 EMI)。 但是、我不知道变压器是不是如此。 请改正我的问题。

谢谢、

Pablo

您好、Pablo、

我们欢迎您的参与、两个并联的 SN6505B 器件的配置可能通过实验工作、但我们无法保证器件不会损坏或其长期可靠性不会受到影响、因此我们不推荐您使用。

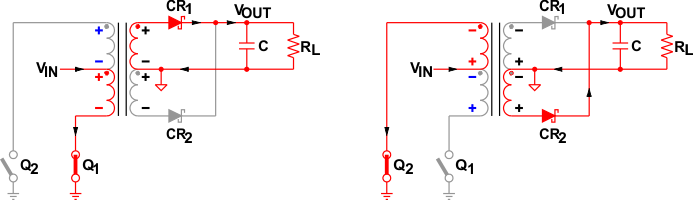

感谢您的解释。 为了使中心抽头变压器正常运行、初级线圈的电压增加到高于 V+电源电压。 SN6505数据表的第8.3.1节(下图)对此进行了说明:

在本说明中、使用 D1/D2到 V+之间的二极管将影响推挽操作;请务必从设计中移除这些二极管、我将更新我之前的响应以反映这一点。

尊敬的、

Manuel Chavez