尊敬的团队:

我不能完全确定不同的偏斜时间在整体偏斜情况下如何一起发挥作用。

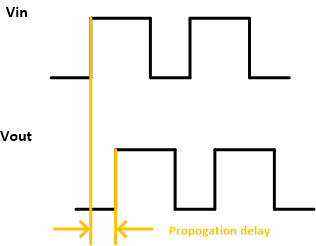

其中一个时间是 t_SK (pp)、即对于给定器件而言、部件间偏移时间为4.4ns。 我读取数据、以便当多个输入在同一方向(HL 或 LH)切换时、最大传播延迟差异将为4.4ns 最慢和最快的传播时间之间的差异。

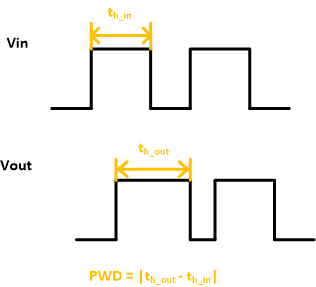

另一个时间是 PWD、即脉宽失真、对于该器件为5ns、描述了 HL 和输入的 LH 变化之间的传播时间差。

对于我来说、这意味着如果部件间偏移处于其极限、并且两个信号在不同方向上切换(一个信号 HL、另一个 LH)并且 PWD 也处于其最大值、则最坏情况下的传播时间差会增加高达9.4ns。

我的假设是否正确或我错过了什么?

此致、

Torsten Lang