工具与软件:

嗨、团队:

我们的客户使用该器件执行了 ESD 测试、并观察到开关停滞时间。

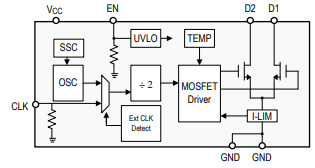

我们猜测这是因为该器件已通过 EN 引脚或 UVLO 启用禁用。

请告诉我们以下问题、

在数据表8.2方框图中、UVLO 块连接了 EN 引脚、但表5-1表明 UVLO 处于 Vcc 描述状态、阈值由 Vcc 电压决定。

在 Vcc 引脚上检测 UVLO 是否正确?

2.如何通过 EN 引脚实现器件启用延迟以及检测到 UVLO 启用延迟?

3.在该数据表8.4.5外部时钟模式中、"该器件还具有外部时钟失效防护功能、如果有效输入时钟长时间不存在、该功能会自动将器件切换到内部时钟(tCLKTIMER )。" 该器件如何检测有效的外部时钟?

EN 引脚和 CLK 引脚由内部电阻器下拉。 两个电阻值的大小是多少?

5.在数据表8.2方框图中、有两个 GND 引脚。 为什么会这样呢?

此致、

Teritama