请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74AVC16T245 工具/软件:

尊敬的团队:

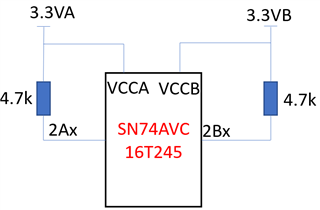

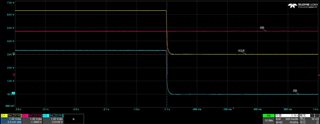

我们将 SN74AVC16T245用于3.3V 至3.3V 缓冲器、OE 和 DIR 引脚拉至低电平、因此信号方向为 CHB 至 CHA。 以3.3V 电源保持 VCCA、我们在 VCCB 侧(3.3VB 电源轨)执行3.3V 断电、我们可以看到2ax 输出在短时间内具有拉低干扰、然后恢复到正常高电平、当发生干扰时、VCCB 电压约为0.6V。 您能帮助我理解为什么这里出现故障吗? 谢谢。