工具/软件:

尊敬的 E2E 团队:

低于要求-

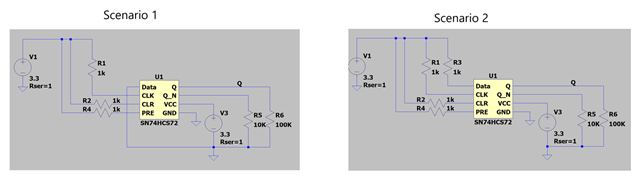

1) 系统存在一个低电平有效错误信号(脉冲:高电平->低电平(100ms)->高电平)输入

2) 根据预定义的规格、可能有单个脉冲或多个脉冲

3)系统要求是有一个用于视觉指示的错误 LED 和错误 LED 应该永久开启在第一个下降沿

4)计划从锁存器驱动错误 LED 使能电路、因为、即使 I/O 引脚上的数据发生变化、锁存器也可以将数据保持在 o/p 处

以下是相关问题:

1)请告知我、上述实现可使用 Weather SN74HCS72?

2)请建议是否有 SN74HCS72以外的合适锁存器 、这可以满足上述要求?

3)是否有其他方式 来 实现上述要求?

此致、

Aditya.