工具/软件:

您好:

我们目前正在设计中使用 SN74LVT162245ADL 在 FPGA 和闪存器件之间发送数据信号。

似乎我们在从闪存读取数据时遇到问题。

因此、FPGA 信号连接在"A"侧、闪存器件连接到"B"侧。

VCCA 为2V5、VCCB 为3V3。 DIR 和 OE 信号由 FPGA 控制。 DIR 1和2共享同一个信号。 OE 也是如此。

因此、当我们发送写入信号(A => B)时、FPGA 信号看起来正确、到闪存的输出看起来也正确。 它已正确翻译。 然而、仅在某些引脚上、我们注意到输出到 FPGA 的数据的错误行为(B => A)。

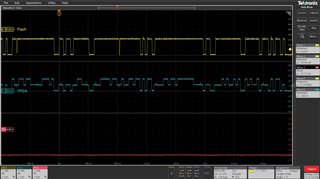

可以在下面看到、B 侧引脚上的 CH1。 CH2是 A 侧的相应引脚。 CH3是 DIR 信号。

以下是我们已经完成的工作:

1.我们更换了设备,但相同的针脚仍然有相同的 issuse

2.我们注意到,在活动操作期间,工作引脚和非工作引脚存在阻抗差异。 工作引脚的电阻约为0.92MOhm、但不工作的电阻约为0.89MOhm。 但我们仅在电路板通电时才看到这种差异。 关断时、工作引脚和非工作引脚之间的电阻测量值相同

3.我们已经尝试了不同的电路板,它连接正确,当我们测量阻抗时,我们得到0.92MOhm 在相同的引脚上不工作的可疑电路板。

谢谢

Albert