请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPLD1202-DYY-EVM 工具/软件:

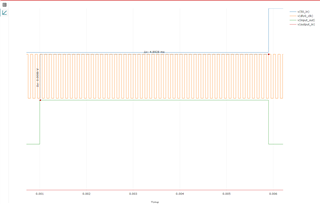

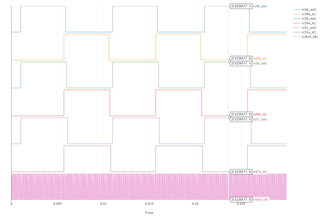

脉冲延迟块显示对脉冲占空比的灵敏度。 我放置了 3 个延迟块、计数为 47。 延迟块的时钟频率为 10kHz。 顶部延迟块在 10ms 的周期内接收到一个占空比为 51%的脉冲。

中间延迟块接收 50%的占空比、底部延迟块接收 49%的占空比。

只有中延迟块(占空比为 50%)会适当延迟脉冲。

Chris Stell