https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1528654/tpld1202-wd-configuration-issue

器件型号:TPLD1202工具/软件:

您好、

我有时间掌握 WD 配置。

我无法让 WD 按预期工作...

我的设计如下:

该延迟用于在复位后的一段时间内阻止看门狗。

我有以下 WD 块配置:

和 WD 刷新仿真参数如下:

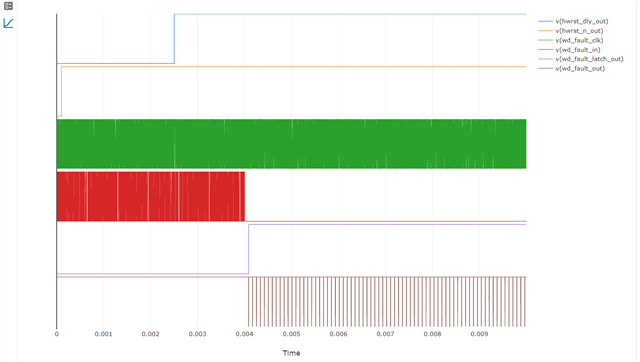

我观察到以下曲线:

如您所见、我正在以 10µs 速率切换刷新输入、并且我已将看门狗配置 100 个 OSC1/2 周期、因此我不会期望 wd 触发故障、但确实会触发故障。

有什么想法吗?

Cl é ment