Other Parts Discussed in Thread: SN74LVC1G04, CSD15380F3

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1528304/sn74lvc1g07-output-configuration

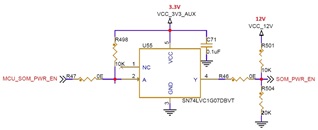

器件型号:SN74LVC1G07主题中讨论的其他器件:SN74LVC1G04、 CSD15380F3

工具/软件:

尊敬的团队:

我在开发板中使用 SN74LVC1G07DBVT 来提供 RESET 信号。 由于 SN74LVC1G07DBVT 是一款开漏同相缓冲器、因此我是否可以在不使用上拉电阻的情况下将引脚 4 (Y) 连接到目标上、从而分别获得高阻抗状态或低电平(对应于输入为高电平或低电平)。 这是一个正确的方法,这是否会影响设备功能 bt 任何机会? 必须在输出侧使用上拉电阻?

此致、

Anoop