Thread 中讨论的其他器件: SN74AUP1G08

工具/软件:

您好、

我正在使用几款 TI 逻辑器件、这些器件声称支持 Ioff 保护和局部断电保护。 我搜索并通读了 TI 和其他供应商网上提供的所有内容、以便尝试更好地了解 Ioff 保护机制的动态。

特别是、当此处引用的 D 型触发器等 IC 将输入引脚连接到可提供相当大电流的低阻抗电压源时、会发生什么情况。 例如锂离子电池、然后 Vcc 引脚从 0 升高到其工作电压相对缓慢。 当 Ioff 激活时、Ioff 功能的规格对于 Vcc 的阈值下限不完全明确。 此外、不知道当 Ioff 停用且器件未达到其最小 Vcc 时在转换区域会发生什么情况、更进一步、即使 Vcc 超过最小 Vcc 导通电压、它仍可能低于 I/O 引脚的电压、我们可能仍会看到 ESD 二极管正向偏置。 在这些条件下、我们实际上在理论上可能会看到 Vcc 和 I/O 引脚之间存在相当大的电压差、并可能会损坏电流。

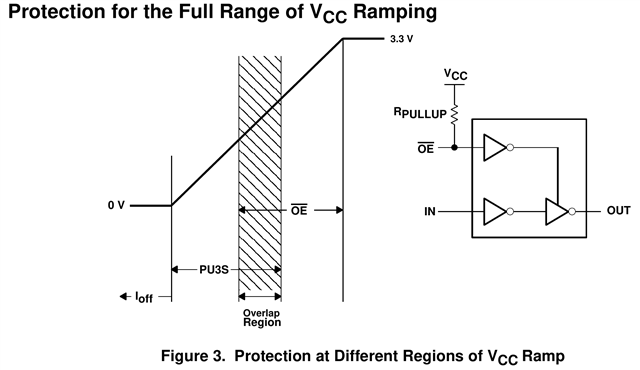

这实际上是真的吗?还是执行了多种保护措施来继续隔离 I/O 引脚、直到 Vcc 超过 I/O 电压? DFLOP 的数据表中没有任何建议、但我已阅读 TI 提供的讨论 PU3S 保护的应用手册。 我不认为 D 触发器有这种机制、但有趣的是、本应用手册中有一个关于 Ioff 的段落有点令人困惑。 我引述。

“对于仅具有 IOFF 规格或没有任何 IOFF、PU3S 和预充电规格的器件(例如 LVC 和 ALVC)、在输出或 I/O 端口暴露于任何带电信号之前、GND 和 VCC 需要上电至建议的工作电平。 如果为该端口指定了 IOFF、则器件输出或 I/O 端口可能会在 VCC = 0V 时暴露于实时信号中。 但具有 IOFF 的输入端口可以在 VCC = 0V 以及 VCC 上升或下降时处理实时信号。 这就是为什么在上电序列中进行 GND 连接之后、只要该端口指定了 Ioff、就可以随时进行输入端口连接。“

这表明输入引脚的行为与输出引脚的行为不同、但这是否正确、这是否仅适用于上述器件系列?

我正在使用其他器件、这些器件也指出它们具有 Ioff 保护、但同样地、在这些情况下、用于保护的阈值电压以及 Vcc 上升或下降时的转换行为以及输入和输出引脚的差异并不完全清楚。

请帮我更详细地说明这些电路的内部结构、具体说明适用的引脚、以及如何阅读数据表以提取任何相关数据、然后我可以决定在哪些情况下需要考虑外部电流限制。 我阅读了 TI 的几个应用手册、甚至还特别提到了数据表中包含的与 Ioff 功能相关的信息、但即使这些手册也无法清楚地回答我的问题。

我期待着有一些澄清,

祝你一切顺利。