工具/软件:

问题 1

我想知道 TXB0104 中的异常振荡原理。

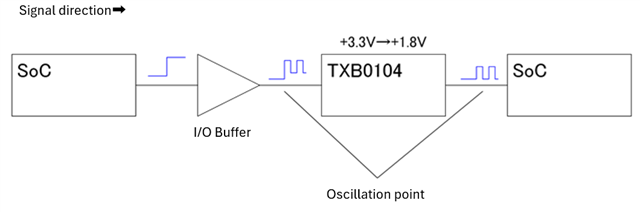

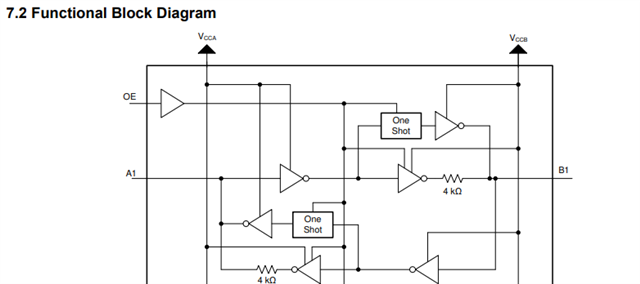

该电路配置为将低电平到高电平信号从 TXB0104 的 IO 缓冲器 (3.3V) 输入到 B#、并将输出从 A#(1.8V) 输出。

A#连接到 SoC 的输入引脚 (Hi-Z)(20kΩ 下拉)。

案例 1:无异常振荡

将 B#从低电平更改为高电平后、将 OE 信号设置为高电平以启用 IC。 此时没有异常振荡、正常启动。

案例 2:异常振荡

将 OE 设为高电平以启用 IC 后、将 B#从低电平更改为高电平。

此时、会发生异常振荡。

请告诉我异常振荡的原理。

连接的波形:CH1-B#信号(黄色)、CH2-A#信号(绿色)、CH3-OE 信号(蓝色)

问题 2.

在问题 1 的第 1 种情况中、如果 B#为高电平、A#为 20kΩ 下拉、并且 OE 信号设置为高电平、将如何确定输入/输出?

此致、