请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1566704/sn74lvc07a-schematic-check

器件型号:SN74LVC07A工具/软件:

尊敬的先生:

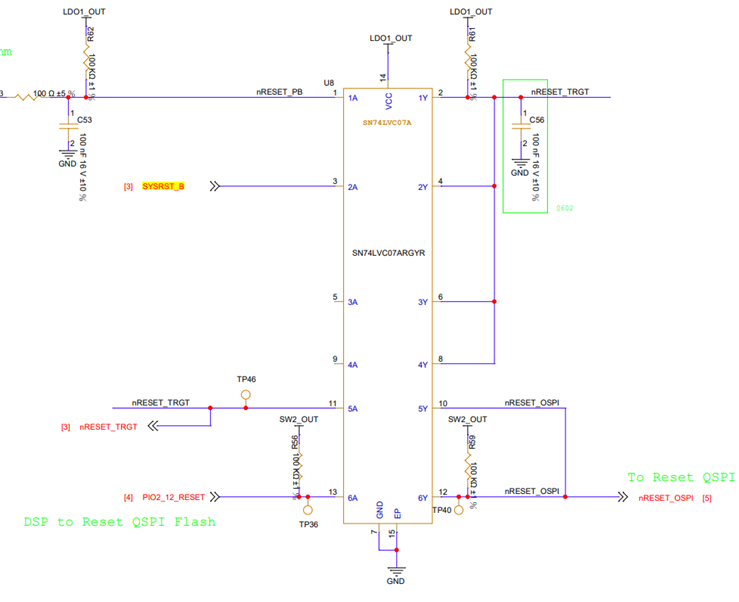

电流测试电路如上所示。

我们发现、当引脚 1/3/13 上的输入信号全部被拉高时、引脚 2/4/12 上测得的输出信号全部为低电平。

当引脚 2 被拉高至 LDO1_OUT (1.8V)、引脚 12 通过电阻器被拉高至 SW2_OUT (1.8V) 时、为什么测量的信号电平为低电平?

请告知这种情况。

谢谢!

此致