器件型号: SN74LV161A

您好、

我在设计中使用了这个 4 位计数器。 我将使用其中的 2 个。 一个由 10MHz 时钟计时、另一个由 5MHz 时钟计时。 电路板设计利用 RCO 输出将其实现为模数 n 计数器。

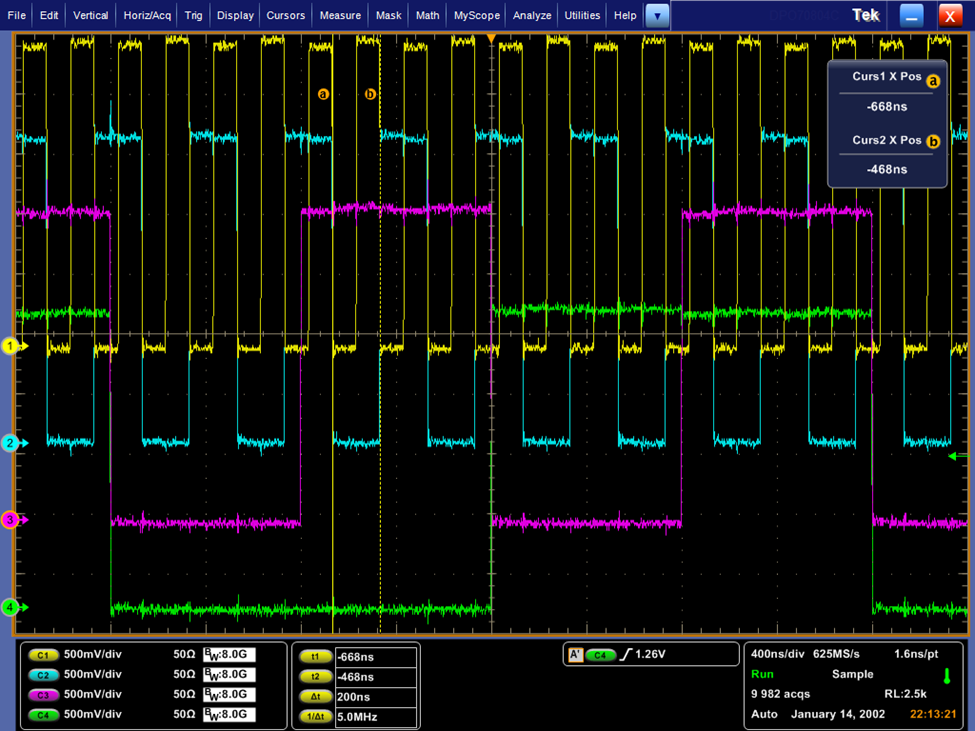

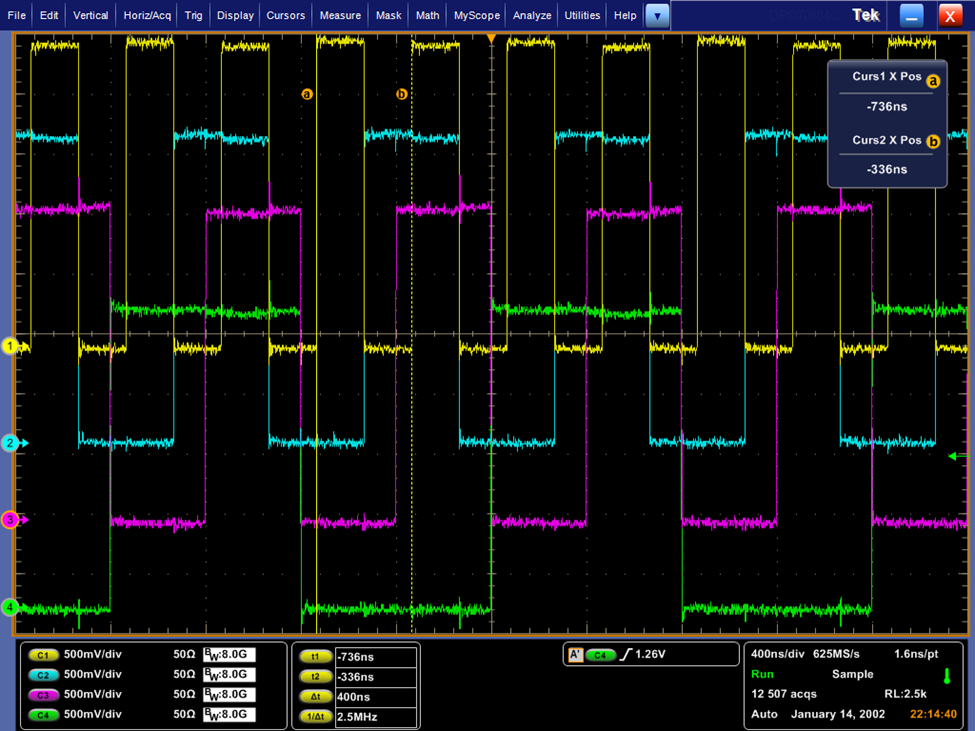

我在板上有错误、我看不到 RCO 脉冲恢复为 LOADB 信号。 但是、计数器似乎在向上计数:

在上述两个图像中、黄色= QA、青色= QB、品红色= QC、绿色= QD。

以上两个屏幕捕获显示 QC 上的过渡相位不匹配、QC 与第二个屏幕中的 QB 匹配。 这是否可以通过 LOADB 信号不正确来解释?

谢谢、

Prasoon