Other Parts Discussed in Thread: TPLD1201, TPLD1201-DGS-EVM

器件型号: TPLD1201

尊敬的 TPLD 员工:

抱歉、我无法显示所有的设计、但是:

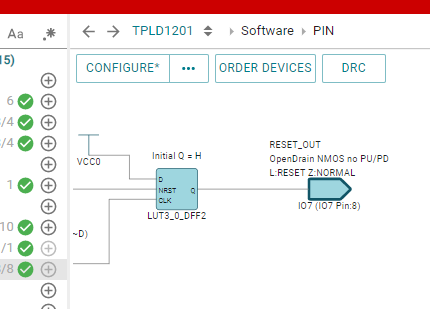

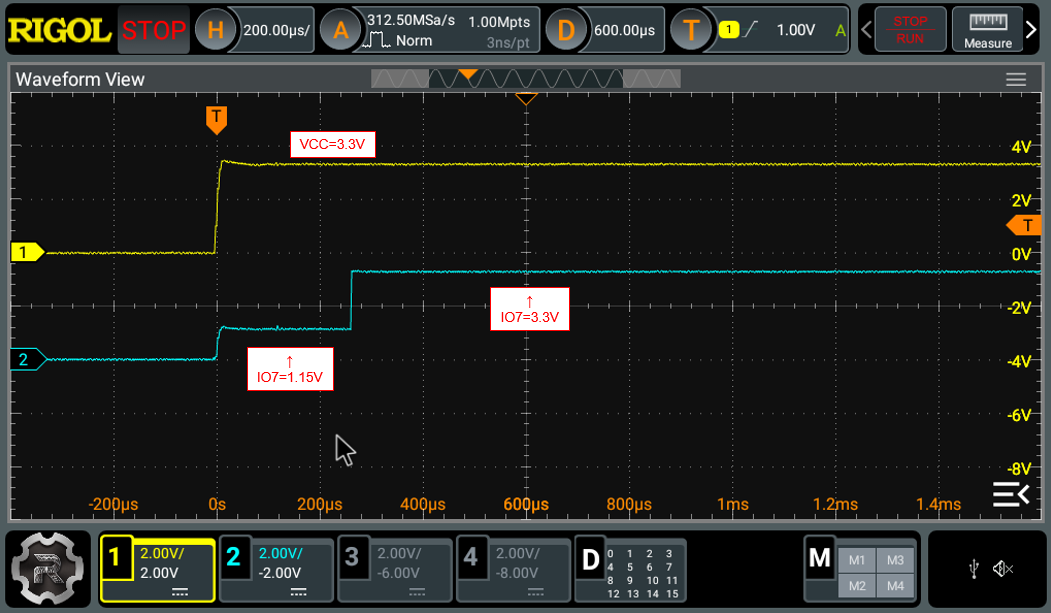

从启动到受控复位事件、IO7 的值应为 Z(表示 H 与外部 PU)。 但烧录 TPLD1201 输出 1.15V:

请注意、IO7 仅将 10k PU 连接到 TPLD 的 VCC。

我可以理解、IO7 在 TPLD 启动期间处于高阻抗状态;245usec。 为什么 IO7 输出 1.15V?

此致、

Okutsu Yasunori